Pętla synchronizacji fazowej - Phase-locked loop

Pętli synchronizacji fazy lub pętlę synchronizacji fazowej ( PLL ) jest system sterowania , która wytwarza sygnał wyjściowy sygnał , którego faza jest związana z fazą sygnału wejściowego. Istnieje kilka różnych typów; najprostszy to układ elektroniczny składający się z oscylatora o zmiennej częstotliwości i detektora fazy w pętli sprzężenia zwrotnego . Oscylator generuje sygnał okresowy, a detektor fazy porównuje fazę tego sygnału z fazą wejściowego sygnału okresowego, dostosowując oscylator tak, aby fazy były dopasowane.

Utrzymywanie fazy wejściowej i wyjściowej w kroku blokady oznacza również utrzymywanie takich samych częstotliwości wejściowych i wyjściowych. W konsekwencji, oprócz synchronizowania sygnałów, pętla synchronizacji fazowej może śledzić częstotliwość wejściową lub może generować częstotliwość będącą wielokrotnością częstotliwości wejściowej. Te właściwości są używane do synchronizacji zegara komputerowego, demodulacji i syntezy częstotliwości .

Pętle synchronizowane fazowo są szeroko stosowane w radiu , telekomunikacji , komputerach i innych aplikacjach elektronicznych. Mogą być używane do demodulacji sygnału, odzyskiwania sygnału z zaszumionego kanału komunikacyjnego, generowania stabilnej częstotliwości o wielokrotności częstotliwości wejściowej ( synteza częstotliwości ) lub dystrybucji precyzyjnie zsynchronizowanych impulsów zegarowych w cyfrowych obwodach logicznych, takich jak mikroprocesory . Ponieważ pojedynczy układ scalony może stanowić kompletny blok konstrukcyjny z pętlą fazową, technika ta jest szeroko stosowana w nowoczesnych urządzeniach elektronicznych, z częstotliwościami wyjściowymi od ułamka herca do wielu gigaherców.

Praktyczne analogie

Analogia do wyścigów samochodowych

Jako analogię PLL rozważ wyścig między dwoma samochodami. Jeden reprezentuje częstotliwość wejściową, a drugi częstotliwość oscylatora sterowanego napięciem (VCO) PLL . Każde okrążenie odpowiada pełnemu cyklowi. Liczba okrążeń na godzinę (prędkość) odpowiada częstotliwości. Oddzielenie samochodów (odległość) odpowiada różnicy faz między dwoma sygnałami oscylacyjnymi.

Przez większość wyścigu każdy samochód jest sam i może swobodnie wyprzedzać drugiego i okrążać drugiego. Jest to analogiczne do PLL w stanie odblokowanym.

Jeśli jednak zdarzy się wypadek, podnoszona jest żółta flaga ostrzegawcza . Oznacza to, że żaden z samochodów wyścigowych nie może wyprzedzać i wyprzedzać drugiego samochodu. Dwa samochody wyścigowe reprezentują częstotliwość wejściową i wyjściową PLL w stanie zablokowanym. Każdy kierowca zmierzy różnicę faz (ułamek dystansu wokół okrążenia) między sobą a innym samochodem wyścigowym. Jeśli tylny kierowca jest zbyt daleko, zwiększą prędkość, aby zmniejszyć dystans. Jeśli są zbyt blisko drugiego samochodu, kierowca zwolni. W rezultacie oba samochody wyścigowe będą okrążać tor w stałym kroku z ustaloną różnicą faz (lub stałą odległością) między nimi. Ponieważ żaden samochód nie może okrążyć drugiego, samochody wykonują taką samą liczbę okrążeń w danym okresie czasu. Dlatego częstotliwość tych dwóch sygnałów jest taka sama.

Analogia do zegara

Faza może być proporcjonalna do czasu, więc różnica faz może być różnicą czasu. Zegary są, z różnym stopniem dokładności, zsynchronizowane fazowo (czasowo) z zegarem prowadzącym.

Pozostawiony sam sobie, każdy zegar będzie odmierzał czas w nieco innym tempie. Na przykład zegar ścienny może być szybszy o kilka sekund na godzinę w porównaniu z zegarem referencyjnym w NIST . Z czasem ta różnica czasu stałaby się znacząca.

Aby zegar ścienny był zsynchronizowany z zegarem referencyjnym, co tydzień właściciel porównuje czas na swoim zegarze ściennym z dokładniejszym zegarem (porównanie fazowe) i resetuje swój zegar. Pozostawiony sam sobie, zegar ścienny będzie nadal odbiegał od zegara referencyjnego w tym samym tempie kilku sekund na godzinę.

Niektóre zegary mają regulację taktowania (kontrola szybka-wolna). Kiedy właściciel porównał czas swojego zegara ściennego z czasem odniesienia, zauważył, że jego zegar był zbyt szybki. W związku z tym właściciel mógł nieco zmienić rozrząd, aby zegar działał trochę wolniej (częstotliwość). Jeśli wszystko pójdzie dobrze, ich zegar będzie dokładniejszy niż wcześniej. Po serii cotygodniowych korekt, pojęcie sekundy zegara ściennego zgadzałoby się z czasem odniesienia (zablokowanym zarówno pod względem częstotliwości, jak i fazy w ramach stabilności zegara ściennego).

Wczesna elektromechaniczna wersja pętli fazowej została zastosowana w 1921 roku w zegarze Shortt-Synchronome .

Historia

Spontaniczną synchronizację słabo sprzężonych zegarów wahadłowych odnotował holenderski fizyk Christiaan Huygens już w 1673 roku. Na przełomie XIX i XX wieku Lord Rayleigh zaobserwował synchronizację słabo sprzężonych piszczałek organowych i kamertonów. W 1919 roku WH Eccles i JH Vincent odkryli, że dwa elektroniczne oscylatory, które zostały dostrojone do oscylacji z nieco innymi częstotliwościami, ale które zostały połączone z obwodem rezonansowym, wkrótce będą oscylować z tą samą częstotliwością. Automatyczna synchronizacja oscylatorów elektronicznych została opisana w 1923 roku przez Edwarda Victora Appletona .

W 1925 roku profesor David Robertson, pierwszy profesor elektrotechniki na Uniwersytecie w Bristolu , wprowadził blokowanie fazy w swoim projekcie zegara, aby kontrolować uderzanie dzwonu Great George w nowym budynku Wills Memorial Building. Zegar Robertsona zawierał urządzenie elektromechaniczne, które mogło zmieniać szybkość oscylacji wahadła i wyprowadzał sygnały korekcyjne z obwodu, który porównywał fazę wahadła z przychodzącym impulsem telegraficznym z Obserwatorium Greenwich każdego ranka o godzinie 10.00 GMT. Oprócz włączenia odpowiedników każdego elementu nowoczesnego elektronicznego PLL, system Robertsona wyróżniał się tym, że jego detektor fazy był implementacją logiki przekaźnikowej detektora fazy/częstotliwości nie widzianego w obwodach elektronicznych do lat 70. XX wieku. Praca Robertsona poprzedzały badania w kierunku tego, co zostało później nazwane pętli faza-lock w 1932 roku, kiedy brytyjscy naukowcy opracowali alternatywę dla Edwin Armstrong „s odbiornik superheterodynowy , w homodynowymi lub odbiornika bezpośrednią konwersję . W systemie homodynowym lub synchrodynowym lokalny oscylator był dostrajany do żądanej częstotliwości wejściowej i mnożony przez sygnał wejściowy. Otrzymany sygnał wyjściowy zawierał oryginalną informację o modulacji. Celem było opracowanie alternatywnego obwodu odbiornika, który wymagałby mniej obwodów strojonych niż odbiornik superheterodynowy. Ponieważ lokalny oscylator gwałtownie dryfowałby w częstotliwości, do oscylatora zastosowano automatyczny sygnał korekcyjny, utrzymując go w tej samej fazie i częstotliwości pożądanego sygnału. Technika została opisana w 1932 r. w artykule Henri de Bellescize we francuskim czasopiśmie L'Onde Électrique .

W analogowych odbiornikach telewizyjnych od co najmniej późnych lat 30. XX wieku obwody z pętlą fazową z pętlą poziomą i pionową są zablokowane w celu synchronizacji impulsów w sygnale rozgłoszeniowym.

Kiedy Signetics wprowadził linię monolitycznych układów scalonych, takich jak NE565, które były kompletnymi systemami pętli fazowej na chipie w 1969, aplikacje dla tej techniki zwielokrotniły się. Kilka lat później RCA wprowadziła układ CMOS Micropower Phase-Locked Loop " CD4046 " , który stał się popularnym układem scalonym.

Struktura i funkcja

Mechanizmy pętli fazowej mogą być realizowane jako obwody analogowe lub cyfrowe. Obie implementacje wykorzystują tę samą podstawową strukturę. Obwody analogowego PLL składają się z czterech podstawowych elementów:

- Detektor fazy ,

- Filtr dolnoprzepustowy ,

- Oscylator sterowany napięciem i

- ścieżka sprzężenia zwrotnego (która może zawierać dzielnik częstotliwości ).

Wariacje

Istnieje kilka odmian PLL. Niektóre terminy, które są używane, to analogowa pętla synchronizacji fazy (APLL), określana również jako liniowa pętla synchronizacji fazy (LPLL), cyfrowa pętla synchronizacji fazy (DPLL), cała cyfrowa pętla synchronizacji fazy (ADPLL) i faza oprogramowania -zamknięta pętla (SPLL).

- PLL analogowy lub liniowy (APLL)

- Detektor fazy jest mnożnikiem analogowym. Filtr pętli jest aktywny lub pasywny. Wykorzystuje oscylator sterowany napięciem (VCO). Mówi się, że APLL jest typem II, jeśli jego filtr pętli ma funkcję przenoszenia z dokładnie jednym biegunem na początku (patrz również przypuszczenie Egana dotyczące zakresu wciągania APLL typu II ).

- Cyfrowy PLL (DPLL)

- Analogowy PLL z cyfrowym detektorem fazy (takim jak XOR, wyzwalacz zboczem JK, detektor częstotliwości fazy). Może mieć w pętli dzielnik cyfrowy.

- Wszystkie cyfrowe PLL (ADPLL)

- Detektor fazy, filtr i oscylator są cyfrowe. Wykorzystuje oscylator sterowany numerycznie (NCO).

- Oprogramowanie PLL (SPLL)

- Bloki funkcjonalne są implementowane przez oprogramowanie, a nie przez specjalistyczny sprzęt.

- Pompa ładująca PLL (CP-PLL)

- CP-PLL to modyfikacja pętli fazowych z detektorem fazowo-częstotliwościowym i sygnałami o przebiegu prostokątnym. Zobacz także przypuszczenie Gardnera na temat CP-PLL .

Parametry wydajności

- Rodzaj i kolejność.

- Zakresy częstotliwości : zakres zatrzymania (zakres śledzenia), zakres wciągania (zakres przechwytywania, zakres akwizycji), zakres blokady. Zobacz także problem Gardnera dotyczący zakresu zamykania , przypuszczenia Egana dotyczące zakresu wciągania APLL typu II .

- Przepustowość pętli: Definiowanie szybkości pętli sterowania.

- Odpowiedź przejściowa: jak czas przeregulowania i ustalania z określoną dokładnością (np. 50 ppm).

- Błędy stanu ustalonego: Jak pozostała faza lub błąd synchronizacji.

- Czystość widma wyjściowego: Jak wstęgi boczne generowane z pewnego tętnienia napięcia strojenia VCO.

- Szum fazowy: Zdefiniowany przez energię szumu w pewnym paśmie częstotliwości (np. przesunięcie 10 kHz od nośnej). Wysoce zależny od szumu fazowego VCO, przepustowości PLL itp.

- Parametry ogólne: takie jak pobór mocy, zakres napięcia zasilania, amplituda wyjściowa itp.

Aplikacje

Pętle synchronizacji fazowej są szeroko stosowane do celów synchronizacji ; w komunikacji kosmicznej dla koherentnej demodulacji i rozszerzenia progu , synchronizacji bitowej i synchronizacji symboli. Pętle z synchronizacją fazową mogą być również wykorzystywane do demodulacji sygnałów o modulowanej częstotliwości. W nadajnikach radiowych PLL jest używany do syntezy nowych częstotliwości, które są wielokrotnością częstotliwości odniesienia, z taką samą stabilnością jak częstotliwość odniesienia.

Inne aplikacje obejmują

- Demodulacji z modulacją częstotliwości (FM): W przypadku PLL jest zablokowana na sygnał FM, VCO tory chwilową częstotliwość sygnału wejściowego. Filtrowane napięcie błędu, które steruje VCO i utrzymuje blokadę z sygnałem wejściowym, jest demodulowane na wyjściu FM. Charakterystyki przenoszenia VCO określają liniowość demodulowanego wyjścia. Ponieważ VCO stosowany w układzie PLL z układem scalonym jest wysoce liniowy, możliwe jest zrealizowanie wysoce liniowych demodulatorów FM.

- Demodulacja kluczowania z przesunięciem częstotliwości (FSK): W cyfrowej transmisji danych i komputerowych urządzeniach peryferyjnych dane binarne są przesyłane za pomocą częstotliwości nośnej, która jest przesuwana między dwiema ustawionymi częstotliwościami.

- Odzyskiwanie małych sygnałów, które w przeciwnym razie zostałyby utracone w szumie ( wzmacniacz blokujący do śledzenia częstotliwości odniesienia)

- Odzyskiwanie informacji o taktowaniu zegara ze strumienia danych, na przykład z dysku twardego

- Mnożniki zegara w mikroprocesorach, które pozwalają wewnętrznym elementom procesora działać szybciej niż połączenia zewnętrzne, przy jednoczesnym zachowaniu precyzyjnych zależności czasowych

- Demodulacja modemów i innych sygnałów tonowych dla telekomunikacji i zdalnego sterowania .

- DSP z wideo sygnałów; Pętle z blokadą fazy są również używane do synchronizacji fazy i częstotliwości z wejściowym analogowym sygnałem wideo , dzięki czemu można go próbkować i przetwarzać cyfrowo

- Mikroskopia sił atomowych w trybie modulacji częstotliwości do wykrywania zmian częstotliwości rezonansowej wspornika w wyniku interakcji końcówka-powierzchnia

- Napęd silnika prądu stałego

Odzyskiwanie zegara

Niektóre strumienie danych, zwłaszcza strumienie danych szeregowych o dużej szybkości (takie jak surowy strumień danych z głowicy magnetycznej dysku), są przesyłane bez towarzyszącego zegara. Odbiornik generuje zegar z przybliżonej częstotliwości odniesienia, a następnie wyrównuje fazę z przejściami w strumieniu danych za pomocą PLL. Proces ten jest nazywany odzyskiwaniem zegara . Aby ten schemat działał, strumień danych musi mieć przejście wystarczająco często, aby skorygować wszelkie dryfty oscylatora PLL. Zazwyczaj jakiś rodzaj kodu liniowego , taki jak kodowanie 8b/10b , jest używany do ustawienia sztywnej górnej granicy maksymalnego czasu między przejściami.

Przekrzywianie

Jeśli zegar jest wysyłany równolegle z danymi, zegar ten może być używany do próbkowania danych. Ponieważ zegar musi zostać odebrany i wzmocniony, zanim będzie mógł sterować przerzutnikami, które próbkują dane, wystąpi skończone i zależne od procesu, temperatury i napięcia opóźnienie między wykrytą krawędzią zegara a odebranym oknem danych. To opóźnienie ogranicza częstotliwość, z jaką dane mogą być wysyłane. Jednym ze sposobów wyeliminowania tego opóźnienia jest uwzględnienie skosu PLL po stronie odbiorczej, tak aby zegar na każdym przerzucie danych był dopasowany fazowo do odebranego zegara. W tego typu aplikacjach często używana jest specjalna forma PLL zwana pętlą z blokadą opóźnienia (DLL).

Generacja zegara

Wiele systemów elektronicznych zawiera różnego rodzaju procesory, które działają z częstotliwością setek megaherców. Zazwyczaj zegary dostarczane do tych procesorów pochodzą z generatorów zegara PLL, które zwielokrotniają zegar odniesienia o niższej częstotliwości (zwykle 50 lub 100 MHz) do częstotliwości roboczej procesora. Współczynnik mnożenia może być dość duży w przypadkach, gdy częstotliwość robocza wynosi wiele gigaherców, a kryształ odniesienia ma tylko dziesiątki lub setki megaherców.

Rozszerzać zakres

Wszystkie systemy elektroniczne emitują niepożądaną energię o częstotliwości radiowej. Różne agencje regulacyjne (takie jak FCC w Stanach Zjednoczonych) nakładają limity na emitowaną energię i wszelkie zakłócenia przez nią powodowane. Emitowany szum na ogół pojawia się w ostrych szczytach widmowych (zwykle przy częstotliwości roboczej urządzenia i kilku harmonicznych). Projektant systemu może użyć PLL o rozłożonym widmie, aby zmniejszyć zakłócenia z odbiornikami o wysokiej Q poprzez rozproszenie energii na większą część widma. Na przykład, zmieniając częstotliwość roboczą w górę i w dół o niewielką wartość (około 1%), urządzenie pracujące z częstotliwością setek megaherców może równomiernie rozłożyć swoje zakłócenia na kilka megaherców widma, co drastycznie zmniejsza ilość szumu widzianego w transmisji Kanały radiowe FM o przepustowości kilkudziesięciu kiloherców.

Dystrybucja zegara

Zazwyczaj zegar odniesienia wchodzi do układu scalonego i steruje pętlą synchronizacji fazowej ( PLL ), która następnie steruje dystrybucją zegara systemowego. Rozkład zegara jest zwykle zrównoważony, dzięki czemu zegar dociera do każdego punktu końcowego jednocześnie. Jednym z tych punktów końcowych jest wejście sprzężenia zwrotnego PLL. Funkcją PLL jest porównywanie rozproszonego zegara z przychodzącym zegarem odniesienia i zmienianie fazy i częstotliwości jego wyjścia, aż zegary odniesienia i sprzężenia zwrotnego zostaną dopasowane w fazie i częstotliwości.

PLL są wszechobecne — dostrajają zegary w systemach o szerokości kilku stóp, a także zegary w małych porcjach pojedynczych chipów. Czasami zegar odniesienia może wcale nie być czystym zegarem, ale raczej strumieniem danych z wystarczającą liczbą przejść, aby PLL była w stanie odzyskać normalny zegar z tego strumienia. Czasami zegar odniesienia ma tę samą częstotliwość, co zegar sterowany rozkładem zegara, innym razem zegar rozproszony może być racjonalną wielokrotnością odniesienia.

Wykrywanie AM

PLL może być wykorzystana do synchronicznej demodulacji sygnałów z modulacją amplitudy (AM). PLL odzyskuje fazę i częstotliwość nośnej przychodzącego sygnału AM. Odzyskana faza w VCO różni się od fazy nośnej o 90 °, więc jest przesuwana w fazie, aby dopasować, a następnie podawana do mnożnika. Wyjście mnożnika zawiera zarówno sumę, jak i sygnały częstotliwości różnicowej, a demodulowane wyjście jest uzyskiwane przez filtrowanie dolnoprzepustowe. Ponieważ PLL reaguje tylko na częstotliwości nośne, które są bardzo zbliżone do wyjścia VCO, detektor PLL AM wykazuje wysoki stopień selektywności i odporności na zakłócenia, co nie jest możliwe w przypadku konwencjonalnych demodulatorów AM typu szczytowego. Jednak pętla może stracić blokadę, gdy sygnały AM mają 100% głębokość modulacji.

Redukcja drgań i szumów

Jedną z pożądanych właściwości wszystkich PLL jest to, że krawędzie zegara odniesienia i sprzężenia zwrotnego są bardzo blisko wyrównane. Średnia różnica czasu między fazami dwóch sygnałów, gdy PLL osiągnęła blokadę, nazywana jest statycznym przesunięciem fazy (zwanym również błędem fazy stanu ustalonego ). Różnica między tymi fazami nazywana jest drganiem śledzenia . Idealnie, przesunięcie fazy statycznej powinno wynosić zero, a fluktuacja śledzenia powinna być jak najniższa.

Szum fazowy jest innym rodzajem jittera obserwowanym w PLL i jest powodowany przez sam oscylator oraz elementy używane w obwodzie sterowania częstotliwością oscylatora. Wiadomo, że niektóre technologie działają pod tym względem lepiej niż inne. Najlepsze cyfrowe PLL są zbudowane z elementów logicznych sprzężonych z emiterem ( ECL ), kosztem wysokiego zużycia energii. Aby utrzymać niski poziom szumów fazowych w obwodach PLL, najlepiej jest unikać nasycania rodzin logicznych, takich jak logika tranzystorowo-tranzystorowa ( TTL ) lub CMOS .

Inną pożądaną właściwością wszystkich PLL jest to, że na fazę i częstotliwość generowanego zegara nie mają wpływu gwałtowne zmiany napięć w liniach zasilających i uziemiających, a także napięcie podłoża, na którym wytwarzane są obwody PLL. Nazywa się to tłumieniem szumów podłoża i zasilania . Im wyższa eliminacja szumów, tym lepiej.

Aby jeszcze bardziej poprawić szum fazowy na wyjściu, oscylator z blokadą wtrysku może być zastosowany po VCO w PLL.

Synteza częstotliwości

W cyfrowych systemach komunikacji bezprzewodowej (GSM, CDMA itp.) PLL są wykorzystywane do zapewnienia konwersji w górę lokalnego oscylatora podczas transmisji i konwersji w dół podczas odbioru. W większości telefonów komórkowych funkcja ta została w dużej mierze zintegrowana w pojedynczym układzie scalonym, aby zmniejszyć koszt i rozmiar telefonu. Jednak ze względu na wysoką wydajność wymaganą od terminali stacji bazowych, obwody nadawcze i odbiorcze są zbudowane z dyskretnych elementów, aby osiągnąć wymagany poziom wydajności. Moduły lokalnych oscylatorów GSM są zazwyczaj zbudowane z układu scalonego syntezatora częstotliwości i VCO z dyskretnym rezonatorem.

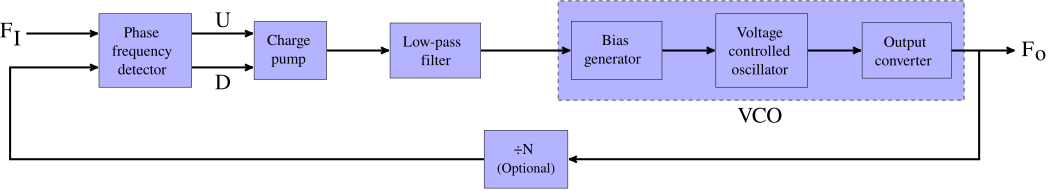

Schemat blokowy

Detektor fazy porównuje dwa sygnały wejściowe i wytwarza sygnał błędu, który jest proporcjonalny do ich różnicy faz. Sygnał błędu jest następnie filtrowany dolnoprzepustowo i wykorzystywany do sterowania VCO, który tworzy fazę wyjściową. Wyjście jest podawane przez opcjonalny rozdzielacz z powrotem do wejścia systemu, tworząc pętlę ujemnego sprzężenia zwrotnego . Jeśli faza wyjściowa dryfuje, sygnał błędu wzrośnie, napędzając fazę VCO w przeciwnym kierunku, aby zmniejszyć błąd. W ten sposób faza wyjściowa jest połączona z fazą na drugim wejściu. To wejście nazywa się referencją.

Analogowe pętle synchronizacji fazowej są zazwyczaj budowane z analogowym detektorem fazy, filtrem dolnoprzepustowym i VCO umieszczonymi w konfiguracji z ujemnym sprzężeniem zwrotnym . Cyfrowa pętla synchronizacji fazy wykorzystuje cyfrowy detektor fazy; może również mieć dzielnik w ścieżce sprzężenia zwrotnego lub w ścieżce odniesienia, lub w obu, aby częstotliwość sygnału wyjściowego PLL była racjonalną wielokrotnością częstotliwości odniesienia. Niecałkowitą wielokrotność częstotliwości odniesienia można również utworzyć, zastępując prosty licznik dzielenia przez N w ścieżce sprzężenia zwrotnego programowalnym licznikiem połykania impulsów . Ta technika jest zwykle nazywana syntezatorem ułamkowym N lub PLL ułamkowym N.

Oscylator generuje okresowy sygnał wyjściowy. Załóżmy, że początkowo oscylator ma prawie taką samą częstotliwość jak sygnał odniesienia. Jeśli faza z oscylatora spada za fazą odniesienia, detektor fazy zmienia napięcie sterujące oscylatora tak, że przyspiesza. Podobnie, jeśli faza przesuwa się przed odniesieniem, detektor fazy zmienia napięcie sterujące, aby spowolnić oscylator. Ponieważ początkowo oscylator może znajdować się daleko od częstotliwości odniesienia, praktyczne detektory fazy mogą również reagować na różnice częstotliwości, aby zwiększyć zakres blokady dopuszczalnych wejść. W zależności od zastosowania, albo wyjście sterowanego oscylatora, albo sygnał sterujący do oscylatora, zapewnia użyteczne wyjście układu PLL.

Elementy

Detektor fazy

Detektor fazy (PD) generuje napięcie, które reprezentuje różnicę faz między dwoma sygnałami. W PLL dwa wejścia detektora fazy są wejściem odniesienia i sprzężeniem zwrotnym z VCO. Napięcie wyjściowe PD służy do sterowania VCO w taki sposób, że różnica faz między dwoma wejściami jest utrzymywana na stałym poziomie, co czyni go systemem ujemnego sprzężenia zwrotnego.

Różne typy detektorów fazy mają różne charakterystyki działania.

Na przykład mikser częstotliwości wytwarza harmoniczne, które zwiększają złożoność aplikacji, w których ważna jest czystość widmowa sygnału VCO. Powstałe niechciane (fałszywe) wstęgi boczne, zwane również „ ostrogami odniesienia ”, mogą zdominować wymagania filtra i zmniejszyć zakres przechwytywania znacznie poniżej lub wydłużyć czas blokowania poza wymagania. W tych zastosowaniach stosuje się bardziej złożone cyfrowe detektory fazy, które nie mają tak silnego elementu odniesienia na wyjściu. Również, gdy jest w zamku, różnica faz w stanie ustalonym na wejściach wykorzystujących ten typ detektora fazy jest bliska 90 stopni.

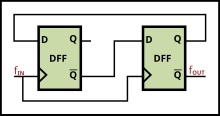

W aplikacjach PLL często wymagana jest wiedza, kiedy pętla nie działa. Bardziej złożone cyfrowe detektory fazowo-częstotliwościowe mają zwykle wyjście, które umożliwia wiarygodne wskazanie stanu braku blokady.

Bramka XOR jest często używana w cyfrowych PLL jako skuteczny, ale prosty detektor fazy. Może być również używany w sensie analogowym z niewielką modyfikacją obwodów.

Filtr

Blok powszechnie nazywany filtrem pętli PLL (zazwyczaj filtrem dolnoprzepustowym) ma zasadniczo dwie różne funkcje.

Podstawową funkcją jest określenie dynamiki pętli, zwanej również stabilnością . W ten sposób pętla reaguje na zakłócenia, takie jak zmiany częstotliwości odniesienia, zmiany dzielnika sprzężenia zwrotnego lub podczas uruchamiania. Typowe rozważania to zakres, w którym pętla może osiągnąć blokadę (zakres wciągania, zakres blokowania lub zasięg przechwytywania), jak szybko pętla osiąga blokadę (czas blokowania, czas blokowania lub czas ustalania ) oraz zachowanie tłumienia . W zależności od zastosowania, może to wymagać jednego lub więcej z następujących elementów: prosta proporcja (wzmocnienie lub tłumienie), całka (filtr dolnoprzepustowy) i/lub pochodna ( filtr górnoprzepustowy ). Badane parametry pętli powszechnie za to są pętli na margines wzmocnienia i margines fazy . Do zaprojektowania tej funkcji wykorzystywane są wspólne koncepcje w teorii sterowania, w tym regulator PID .

Drugim powszechnym czynnikiem jest ograniczenie ilości energii częstotliwości odniesienia (tętnienia) pojawiającej się na wyjściu detektora fazy, która jest następnie doprowadzana do wejścia sterującego VCO. Ta częstotliwość moduluje VCO i wytwarza wstęgi boczne FM powszechnie nazywane „ostrogami odniesienia”.

Projekt tego bloku może być zdominowany przez którekolwiek z tych rozważań lub może być złożonym procesem żonglującym interakcjami tych dwóch. Typowe kompromisy polegają na tym, że zwiększenie przepustowości zwykle pogarsza stabilność lub zbyt duże tłumienie dla lepszej stabilności zmniejszy prędkość i wydłuży czas ustalania. Często wpływa to również na szum fazowy.

Oscylator

Wszystkie pętle synchronizacji fazowej wykorzystują element oscylatora o zmiennej częstotliwości. Może to być analogowy VCO sterowany obwodami analogowymi w przypadku APLL lub sterowany cyfrowo za pomocą przetwornika cyfrowo-analogowego, jak w przypadku niektórych projektów DPLL. W ADPLL stosowane są w pełni cyfrowe oscylatory, takie jak oscylator sterowany numerycznie.

Ścieżka informacji zwrotnej i opcjonalny rozdzielacz

PLL mogą zawierać dzielnik między oscylatorem a wejściem sprzężenia zwrotnego do detektora fazy w celu wytworzenia syntezatora częstotliwości . Programowalny dzielnik jest szczególnie przydatny w zastosowaniach nadajników radiowych, ponieważ duża liczba częstotliwości transmisji może być wytworzona z jednego stabilnego, dokładnego, ale drogiego oscylatora odniesienia sterowanego kryształem kwarcu .

Niektóre PLL zawierają również dzielnik między zegarem odniesienia a wejściem odniesienia detektora fazy. Jeśli dzielnik w ścieżce sprzężenia zwrotnego dzieli się przez, a dzielnik wejścia odniesienia dzieli przez , umożliwia to PLL pomnożenie częstotliwości odniesienia przez . Może wydawać się prostsze, aby po prostu zasilić PLL niższą częstotliwością, ale w niektórych przypadkach częstotliwość odniesienia może być ograniczona przez inne kwestie, a wtedy dzielnik odniesienia jest przydatny.

Mnożenie częstotliwości można również osiągnąć poprzez zablokowanie wyjścia VCO do N- tej harmonicznej sygnału odniesienia. Zamiast prostego detektora fazy w konstrukcji zastosowano mikser harmoniczny (mikser próbkowania). Mikser harmonicznych zamienia sygnał odniesienia w ciąg impulsów bogaty w harmoniczne. Wyjście VCO jest zgrubnie dostrojone, aby było zbliżone do jednej z tych harmonicznych. W konsekwencji żądana wartość wyjściowa miksera harmonicznych (reprezentująca różnicę między harmoniczną N a wyjściem VCO) mieści się w paśmie przepustowym filtra pętli.

Należy również zauważyć, że sprzężenie zwrotne nie ogranicza się do dzielnika częstotliwości. Elementem tym mogą być inne elementy, takie jak mnożnik częstotliwości lub mikser. Mnożnik sprawi, że wyjście VCO będzie podwielokrotnością (a nie wielokrotnością) częstotliwości odniesienia. Mikser może przełożyć częstotliwość VCO o stałe przesunięcie. Może to być również kombinacja tych. Przykładem jest dzielnik podążający za mikserem; pozwala to dzielnikowi działać przy znacznie niższej częstotliwości niż VCO bez utraty wzmocnienia pętli.

Modelowanie

Model domeny czasu APPL

Równania rządzące pętlą synchronizacji fazowej z analogowym mnożnikiem jako detektorem fazy i filtrem liniowym można wyprowadzić w następujący sposób. Niech wejście do detektora fazy będzie i wyjście VCO będzie z fazami i . Funkcje i opisują przebiegi sygnałów. Wtedy wyjście detektora fazy jest podane przez

Częstotliwość VCO jest zwykle traktowana jako funkcja wejścia VCO jako

gdzie jest czułość VCO i jest wyrażona w Hz / V; to wolna częstotliwość VCO.

Filtr pętli można opisać układem liniowych równań różniczkowych

gdzie jest wejściem filtra, wyjściem filtra, jest -by- macierzą, . reprezentuje stan początkowy filtra. Symbol gwiazdy jest transpozycją sprzężoną .

Stąd następujący system opisuje PLL

gdzie jest początkowe przesunięcie fazowe.

Model domeny fazowej APPL

Weź pod uwagę, że wejścia PLL i VCO są sygnałami o wysokiej częstotliwości. Następnie dla dowolnych odcinkowo różniczkowalnych -okresowych funkcji i istnieje funkcja taka, że wyjście Filtra

w domenie fazowej jest asymptotycznie równy (różnica jest niewielka w odniesieniu do częstotliwości) do wyjścia filtra w modelu w domenie czasu. Tutaj funkcją jest charakterystyka detektora fazy .

Oznacz przez różnicę faz

Następnie następujący system dynamiczny opisuje zachowanie PLL:

Tutaj ; to częstotliwość oscylatora odniesienia (zakładamy, że jest stała).

Przykład

Rozważ sygnały sinusoidalne

oraz prosty jednobiegunowy obwód RC jako filtr. Model w dziedzinie czasu przyjmuje postać

Charakterystyka wyładowań niezupełnych dla tych sygnałów jest równa

Stąd model domeny fazowej przyjmuje postać

Ten układ równań jest równoważny równaniu wahadła matematycznego

Zlinearyzowany model domeny fazy

Pętle synchronizacji fazowej mogą być również analizowane jako systemy sterowania poprzez zastosowanie transformacji Laplace'a . Odpowiedź pętli można zapisać jako

Gdzie

- to faza wyjściowa w radianach

- jest fazą wejściową w radianach

- jest wzmocnienie detektora fazy w woltach na radian

- jest zysk VCO w radianach na volt- sekundę

- to funkcja przenoszenia filtra pętli (bezwymiarowa)

Charakterystyki pętli można kontrolować, wstawiając różne typy filtrów pętli. Najprostszym filtrem jest jednobiegunowy obwód RC . Funkcja przenoszenia pętli w tym przypadku to

Odpowiedź pętli staje się:

Jest to forma klasycznego oscylatora harmonicznego . Mianownik może być powiązany z mianownikiem systemu drugiego rzędu:

gdzie jest współczynnikiem tłumienia i częstotliwością własną pętli.

Dla jednobiegunowego filtra RC,

Częstotliwość drgań własnych pętli jest miarą czasu odpowiedzi pętli, a współczynnik tłumienia jest miarą przeregulowania i dzwonienia. W idealnym przypadku częstotliwość drgań własnych powinna być wysoka, a współczynnik tłumienia powinien być bliski 0,707 (tłumienie krytyczne). Przy filtrze jednobiegunowym nie jest możliwe niezależne sterowanie częstotliwością pętli i współczynnikiem tłumienia. W przypadku krytycznego tłumienia,

Nieco bardziej skuteczny filtr, filtr lag-lead zawiera jeden biegun i jedno zero. Można to zrealizować za pomocą dwóch rezystorów i jednego kondensatora. Funkcja transferu dla tego filtra to

Ten filtr ma dwie stałe czasowe

Zastąpienie powyższego daje następującą częstotliwość drgań własnych i współczynnik tłumienia

Składniki filtra pętli można obliczyć niezależnie dla danej częstotliwości drgań własnych i współczynnika tłumienia

Konstrukcja filtra pętli w świecie rzeczywistym może być znacznie bardziej skomplikowana, np. użycie filtrów wyższego rzędu w celu zmniejszenia różnych typów lub źródeł szumu fazowego. (Patrz ref. D Banerjee poniżej)

Implementacja cyfrowej pętli fazowej w oprogramowaniu

Cyfrowe pętle synchronizacji fazowej mogą być implementowane sprzętowo, przy użyciu układów scalonych, takich jak CMOS 4046. Jednak w miarę jak mikrokontrolery stają się szybsze, sensowne może być wdrożenie pętli synchronizacji fazowej w oprogramowaniu dla aplikacji, które nie wymagają blokowania sygnałów w MHz zakres lub szybszy, np. precyzyjne sterowanie prędkością silnika. Implementacja oprogramowania ma kilka zalet, w tym łatwe dostosowanie pętli sprzężenia zwrotnego, w tym zmianę współczynnika mnożenia lub dzielenia między śledzonym sygnałem a oscylatorem wyjściowym. Ponadto implementacja oprogramowania jest przydatna do zrozumienia i eksperymentowania. Jako przykład pętli synchronizacji fazy zaimplementowanej przy użyciu detektora częstotliwości fazowej przedstawiono w MATLAB, ponieważ ten typ detektora fazy jest solidny i łatwy do wdrożenia.

% This example is written in MATLAB

% Initialize variables

vcofreq = zeros(1, numiterations);

ervec = zeros(1, numiterations);

% Keep track of last states of reference, signal, and error signal

qsig = 0; qref = 0; lref = 0; lsig = 0; lersig = 0;

phs = 0;

freq = 0;

% Loop filter constants (proportional and derivative)

% Currently powers of two to facilitate multiplication by shifts

prop = 1 / 128;

deriv = 64;

for it = 1:numiterations

% Simulate a local oscillator using a 16-bit counter

phs = mod(phs + floor(freq / 2 ^ 16), 2 ^ 16);

ref = phs < 32768;

% Get the next digital value (0 or 1) of the signal to track

sig = tracksig(it);

% Implement the phase-frequency detector

rst = ~ (qsig & qref); % Reset the "flip-flop" of the phase-frequency

% detector when both signal and reference are high

qsig = (qsig | (sig & ~ lsig)) & rst; % Trigger signal flip-flop and leading edge of signal

qref = (qref | (ref & ~ lref)) & rst; % Trigger reference flip-flop on leading edge of reference

lref = ref; lsig = sig; % Store these values for next iteration (for edge detection)

ersig = qref - qsig; % Compute the error signal (whether frequency should increase or decrease)

% Error signal is given by one or the other flip flop signal

% Implement a pole-zero filter by proportional and derivative input to frequency

filtered_ersig = ersig + (ersig - lersig) * deriv;

% Keep error signal for proportional output

lersig = ersig;

% Integrate VCO frequency using the error signal

freq = freq - 2 ^ 16 * filtered_ersig * prop;

% Frequency is tracked as a fixed-point binary fraction

% Store the current VCO frequency

vcofreq(1, it) = freq / 2 ^ 16;

% Store the error signal to show whether signal or reference is higher frequency

ervec(1, it) = ersig;

end

W tym przykładzie zakłada się , że tablica trackig zawiera sygnał odniesienia, który ma być śledzony. Oscylator jest realizowany przez licznik, przy czym najbardziej znaczący bit licznika wskazuje stan włączenia/wyłączenia oscylatora. Ten kod symuluje dwa przerzutniki typu D, które zawierają komparator fazowo-częstotliwościowy. Gdy odniesienie lub sygnał ma dodatnie zbocze, odpowiedni przerzutnik przełącza się w stan wysoki. Gdy poziom odniesienia i sygnału jest wysoki, oba przerzutniki są resetowane. To, który przerzutnik jest wysoki, określa w tej chwili, czy odniesienie lub sygnał prowadzi do drugiego. Sygnał błędu jest różnicą między tymi dwoma wartościami przerzutnika. Filtr biegunowo-zerowy jest realizowany przez dodanie sygnału błędu i jego pochodnej do przefiltrowanego sygnału błędu. To z kolei jest zintegrowane, aby znaleźć częstotliwość oscylatora.

W praktyce można by prawdopodobnie wstawić inne operacje do sprzężenia zwrotnego tej pętli fazowej. Na przykład, jeśli pętla synchronizacji fazowej miałaby implementować mnożnik częstotliwości, sygnał oscylatora mógłby zostać podzielony na częstotliwość przed porównaniem go z sygnałem odniesienia.

Zobacz też

- Pętla z blokadą częstotliwości

- Pętla z blokadą fazową pompy ładującej

- Odzyskiwanie przewoźnika

- Mapa kołowa — prosty model matematyczny pętli synchronizacji fazowej, pokazujący zarówno blokowanie modów, jak i zachowanie chaotyczne.

- Pętla Costas

- Pętla z blokadą opóźnienia (DLL)

- Odbiornik bezpośredniej konwersji

- Bezpośredni syntezator cyfrowy

- Filtr Kalmana

- PLL wielobitowy

- Shortt-Synchronom clock - Slave wahadło synchronizowane fazowo z masterem (ok. 1921)

Uwagi

Bibliografia

Dalsza lektura

- Banerjee, Dean (2006), PLL Performance, Simulation and Design Handbook (wyd. 4), National Semiconductor , zarchiwizowane od oryginału dnia 2012-09-02 , pobrane 2012-12-04.

- Best, RE (2003), Phase-locked Loops: Design, Simulation and Applications , McGraw-Hill, ISBN 0-07-141201-8

- de Bellescize, Henri (czerwiec 1932), "La réception Synchrone", L'Onde Electrique , 11 : 230-240

- Dorf, Richard C. (1993), Podręcznik inżynierii elektrycznej , Boca Raton: CRC Press, Bibcode : 1993eeh..book.....D , ISBN 0-8493-0185-8

- Egan, William F. (1998), Podstawy Phase-Lock , John Wiley & Sons. (zapewnia przydatne skrypty Matlab do symulacji)

- Egan, William F. (2000), Synteza częstotliwości przez Phase Lock (2nd ed.), John Wiley and Sons. (zapewnia przydatne skrypty Matlab do symulacji)

- Gardner, Floyd M. (2005), Techniki Phaselock (3rd ed.), Wiley-Interscience, ISBN 978-0-471-43063-6

- Klapper, J.; Frankle, JT (1972), Systemy sprzężenia fazowego i sprzężenia częstotliwościowego , Prasa akademicka. (Demodulacja FM)

- Kundert, Ken (sierpień 2006), Przewidywanie szumu fazowego i jittera syntezatorów częstotliwości opartych na PLL (PDF) (4g wyd.), Designer's Guide Consulting, Inc.

- Liu, Mingliang (21 lutego 2006), Zbuduj linię projektową sieci bezprzewodowej 1,5 V 2,4 GHz CMOS PLL , zarchiwizowana z oryginału 1 lipca 2010 r.. Artykuł dotyczący projektowania standardowego układu PLL IC dla aplikacji Bluetooth.

- Wolaver, Dan H. (1991), Projektowanie obwodów pętli fazowej , Prentice Hall, ISBN 0-13-662743-9

Zewnętrzne linki

- Podkład z pętlą blokowania fazowego — zawiera osadzone wideo

- Excel Unusual zawiera animowany model PLL i samouczki do kodowania takiego modelu .

![{\ Displaystyle {\ zacząć {wyrównany} {\ kropka {x}} i = - {\ Frac {1} {RC}} x + {\ Frac {1} {RC}} A_ {1} A_ {2} \ grzech (\theta _{1}(t))\cos(\theta _{2}(t)),\\[6pt]{\dot {\theta }}_{2}&=\omega _{\text {wolny}}+g_{v}(c^{*}x)\end{wyrównany}}}](https://wikimedia.org/api/rest_v1/media/math/render/svg/7aa30f8d69878ef11010da5b8a238c9811b425c7)

![{\begin{wyrównany}{\dot x}&=-{\frac {1}{RC}}x+{\frac {1}{RC}}{\frac {A_{1}A_{2}}{2 }}\sin(\theta _{{\Delta }}),\\[6pt]{\dot \theta }_{{\Delta }}&=\omega _{{\Delta }}-g_{v} (c^{{*}}x).\end{wyrównany}}](https://wikimedia.org/api/rest_v1/media/math/render/svg/a27dc4e09c9f27ca06eda5c20cfd62db61852aa9)

![{\begin{wyrównany}x&={\frac {{\dot \theta }_{2}-\omega _{2}}{g_{v}c^{*}}}={\frac {\omega _ {1}-{\dot \theta }_{{\Delta }}-\omega _{2}}{g_{v}c^{*}}},\\[6pt]{\dot x}&= {\frac {{\ddot \theta }_{2}}{g_{v}c^{*}}},\\[6pt]\theta _{1}&=\omega _{1}t+\Psi ,\\[6pt]\theta _{{\Delta }}&=\theta _{1}-\theta _{2},\\[6pt]{\dot \theta }_{{\Delta }}& ={\dot \theta }_{1}-{\dot \theta }_{2}=\omega _{1}-{\dot \theta }_{2},\\[6pt]&{\frac {1}{g_{v}c^{*}}}{\ddot \theta }_{{\Delta }}-{\frac {1}{g_{v}c^{*}RC}}{\ kropka \theta }_{{\Delta }}-{\frac {A_{1}A_{2}}{2RC}}\sin \theta _{{\Delta }}={\frac {\omega _{2 }-\omega _{1}}{g_{v}c^{*}RC}}.\end{wyrównany}}](https://wikimedia.org/api/rest_v1/media/math/render/svg/e270e7df2f932355fbcf2a304ac607c0247b75f7)