Texas Instruments TMS9900 - Texas Instruments TMS9900

| Projektant | Instrumenty Texas |

|---|---|

| Bity | 16-bitowy |

| Wprowadzono | 1976 |

| Projekt | CISC |

| Endianowość | Duża |

| Rejestry | |

| PC, WP, ST | |

| Ogólny cel | 2 wewnętrznie umieszczone w procesorze (WP, ST) 16 × 16-bitowy stos umieszczony w zewnętrznej pamięci RAM |

Wprowadzony na rynek w czerwcu 1976 r. TMS9900 był jednym z pierwszych dostępnych na rynku jednoukładowych 16-bitowych mikroprocesorów . Jest realizowany Texas Instruments ' TI-990 minikomputer architekturę w formacie jednoukładowym i był początkowo używany do modeli low-end tego spisu.

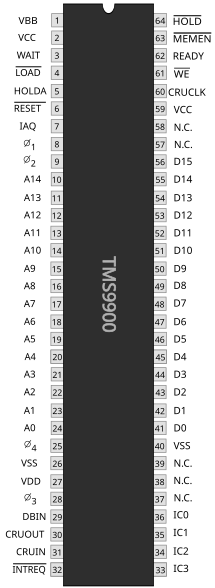

Jego 64-pinowy format DIP sprawił, że jego implementacja w mniejszych maszynach była droższa niż bardziej popularny format 40-pinowy, a ponadto odnotował stosunkowo niewiele wygranych projektów poza własnym użyciem TI. Wśród tych zastosowań był komputer domowy TI-99/4 firmy TI , który ostatecznie sprzedał około 2,8 miliona egzemplarzy.

W połowie lat osiemdziesiątych dziedzina mikrokomputerów przeniosła się na systemy 16-bitowe, takie jak Intel 8088 i nowsze konstrukcje 16/32-bitowe, takie jak Motorola 68000 , które z łatwością przewyższały 9900 i były generalnie tańsze. Nie mając żadnej oczywistej przyszłości dla chipa, firma TI skupiła się na procesorach specjalnego przeznaczenia, takich jak Texas Instruments TMS320 , wprowadzony w 1983 roku.

Historia

TMS9900 został zaprojektowany jako jednoukładowa wersja serii minikomputerów TI 990 , podobnie jak Intersil 6100 był jednoukładowym PDP-8 (12 bitów), a Fairchild 9440 i Data General mN601 były jednoukładowymi wersjami Data General „s Nova . W przeciwieństwie do wieloukładowych 16-bitowych mikroprocesorów, takich jak National Semiconductor IMP-16 czy DEC LSI-11 , niektóre z nich poprzedzały TMS9900, ten ostatni był jednoukładowym, samodzielnym 16-bitowym mikroprocesorem. Jedyny znany jednoukładowy 16-bitowy projekt, który poprzedza TMS9900, to prawie nieznany Panafacom MN1610 , wydany w 1975 roku.

Korzenie minikomputera TMS9900 dają początek wielu cechom architektonicznym, które nie są powszechnie spotykane w projektach, które zaczynały się od czystej kartki. Wśród nich godne uwagi było wykorzystanie przez TMS9900 rejestrów mapowanych do pamięci głównej . Pozwala to na szybkie przełączanie kontekstu , które można osiągnąć poprzez zmianę pojedynczego wskaźnika, podczas gdy bardziej tradycyjne projekty wymagałyby przechowywania całego zestawu rejestrów wewnętrznych w pamięci lub na stosie. Minusem tego podejścia jest to, że dostęp do tych rejestrów jest bardziej czasochłonny. W implementacji minikomputera efekt jest stosunkowo niewielki, a plus w środowisku wielozadaniowym jest znaczny. W innych rolach, takich jak mikrokomputery dla jednego użytkownika lub systemy wbudowane, ten kompromis może nie być opłacalny.

Firma TI zastosowała tę samą architekturę w różnych działach w celu uzyskania synergii korporacyjnej: „jedna firma, jedna architektura komputerowa”. Pod koniec lat 70. Walden C. Rhines przedstawił TMS9900 grupie IBM opracowującej komputer osobisty. „Do 1981 r. nie wiedzielibyśmy, co straciliśmy”, ponieważ IBM wybrał Intel 8088 dla IBM PC – przypomniał. Po nieudanej próbie, aby dostać się na rynku komputerów osobistych z produktów takich jak TI-99 / 4A , mikroprocesor podział firma ostatecznie włączony ostrość na TMS320 celowej serii procesorów.

Architektura

TMS9900 posiada trzy wewnętrzne 16-bitowe rejestry — licznik programu (PC), rejestr stanu (ST) i rejestr wskaźnika obszaru roboczego (WP). Rejestr WP wskazuje na adres bazowy w zewnętrznej pamięci RAM, gdzie jest przechowywanych 16 rejestrów użytkownika ogólnego przeznaczenia procesora (każdy o szerokości 16 bitów). Architektura ta pozwala na szybkie przełączanie kontekstu ; Np. gdy wprowadzany jest podprogram , tylko jeden rejestr obszaru roboczego musi zostać zmieniony, zamiast konieczności zapisywania rejestrów pojedynczo.

Adresy odnoszą się do bajtów z konwencją porządkowania big endian . TMS9900 to klasyczna 16-bitowa maszyna z przestrzenią adresową 2 16 bajtów (65 536 bajtów lub 32 768 słów).

Nie ma koncepcji stosu ani rejestru wskaźnika stosu. Zamiast tego istnieją instrukcje rozgałęzienia, które zapisują licznik programu w rejestrze i zmieniają kontekst rejestru. Każdy z 16 wektorów przerwań sprzętowych i 16 wektorów przerwań oprogramowania składa się z pary wartości PC i WP, więc przełączenie kontekstu rejestru jest również automatycznie wykonywane przez przerwanie.

Zestaw instrukcji i adresowanie

TMS9900 posiada 69 instrukcji, które mają długość jednego, dwóch lub trzech słów i są zawsze wyrównane do słów w pamięci. Zestaw instrukcji jest dość ortogonalny , co oznacza, że z kilkoma wyjątkami, instrukcje mogą używać wszystkich metod dostępu do operandów (tryb adresowania).

Tryby adresowania obejmują natychmiastowy (operand w instrukcji), bezpośredni lub „symboliczny” (adres argumentu w instrukcji), rejestr (operand w rejestrze obszaru roboczego), rejestr pośredni (adres argumentu w rejestrze obszaru roboczego) z lub bez autoinkrementacji, indeksowany (adres argumentu w instrukcji indeksowanej zawartością rejestru obszaru roboczego) oraz Program Counter Relative.

Najważniejsze instrukcje dwuargumentowe (dodawanie, odejmowanie, porównywanie, przenoszenie itp.) zawierają 2-bitowy tryb adresowania i 4-bitowe pola selektora rejestru zarówno dla operandów źródłowych, jak i docelowych. W opkodzie tryb „Symboliczny” jest reprezentowany jako tryb indeksowany z polem rejestru ustawionym na 0, dlatego rejestr obszaru roboczego 0 (WR0) nie może być używany w trybie indeksowanym. W rzadziej używanych instrukcjach dwuoperandowych, takich jak XOR, operand docelowy musi być rejestrem obszaru roboczego (lub parą rejestrów obszaru roboczego w przypadku instrukcji mnożenia i dzielenia).

Sterowanie przepływem jest ułatwione dzięki grupie jednej bezwarunkowej i dwunastu warunkowych instrukcji skoku. Cele skoku odnoszą się do PC z przesunięciem adresów słów od -128 do +127.

W przypadku wywołań podprogramów instrukcja Branch and Load Workspace Pointer (BLWP) ładuje nowe wartości WP i PC, a następnie zapisuje wartości WP, PC i ST odpowiednio w (nowych) rejestrach 13, 14 i 15. Na końcu podprogramu wskaźnik Return Workspace Pointer (RTWP) przywraca je w odwrotnej kolejności. Korzystając z BLWP/RTWP, możliwe jest zagnieżdżanie wywołań podprogramów pomimo braku stosu, jednak programista musi jawnie przypisać odpowiedni obszar roboczy rejestru.

Zestaw instrukcji zawiera również kod operacji rozgałęzienia i łącza (BL), który zapisuje tylko komputer w rejestrze 11 bez zmiany WP. W tym przypadku instrukcja rozgałęzienia (B) używająca WR11 jako adresu docelowego może służyć jako zwrotny kod operacyjny, ale podprogramy typu BL nie mogą być zagnieżdżone bez podjęcia przez programistę działań mających na celu zapisanie adresu zwrotnego.

TMS9900 obsługuje instrukcję wykonania "X" (eXecute). Ta instrukcja wykonuje instrukcję w rejestrze. Może być używany do debugowania (jako instrukcja punktu przerwania ) i do tworzenia tabel indeksowanych kodów operacyjnych, jak to jest używane w interpreterach kodu bajtowego.

TMS9900 obsługuje również instrukcję eXtended OPeration (XOP). XOP otrzymuje liczbę z zakresu 0-15 oraz adres źródłowy. Po wywołaniu, instrukcja wykona przełączenie kontekstu przez jeden z szesnastu wektorów w predefiniowanych miejscach w pamięci. Jest to podobne do przerwania, ale instrukcja XOP przechowuje również adres źródłowy w rejestrze 11 nowego obszaru roboczego. XOP jest mniej elastyczny niż BLWP, ponieważ wektory transferu muszą znajdować się w stałych lokalizacjach, ale oszczędza pamięć, ponieważ adres źródłowy może być używany przez wykonywaną podprogram, gdy nie definiuje lokalizacji wektora. XOP służy do implementacji instrukcji w oprogramowaniu w niższych modelach, gdzie wyższe wersje minikomputerów z serii 990 mogą mieć dedykowany sprzęt do ich wykonywania.

W typowych porównaniach z Intel 8086 TMS9900 miał mniejsze programy. Jedyne wady to mała przestrzeń adresowa i potrzeba szybkiej pamięci RAM.

Realizacja

TMS9900 został zaimplementowany w N-kanałowym procesie MOS z bramką krzemową, który wymagał zasilaczy +5 V, -5 V i +12 V oraz czterofazowego (nie nakładającego się) zegara o maksymalnej częstotliwości 3 MHz (333 ns). cykl), zwykle generowany z kryształu 48 MHz przy użyciu układu generatora zegara TIM9904 (aka 74LS362).

Najkrótsze instrukcje wymagają ukończenia ośmiu cykli zegara lub 2,7 μs (przy założeniu 0 zewnętrznych cykli oczekiwania), wiele innych działa od 10 do 14 cykli (3,3...4,7 μs); najdłużej działająca instrukcja (DIV) może zająć do 124 cykli (41,3 μs).

Układ został zapakowany w (wtedy nietypowy) 64-pinowy DIP o szerokości 0,9" . Stosunkowo duża liczba pinów pozwoliła na wyprowadzenie 15-bitowej (słowo) szyny adresowej i 16-bitowej szyny danych na dedykowanych pinach bez zastosowanie multipleksacji (w przeciwieństwie do np. procesora Intel 8086 ), utrzymując proste połączenia pamięci zewnętrznej.W przeciwieństwie do konwencji stosowanej przez wielu innych producentów, TI oznaczyło najważniejsze linie adresu i danych odpowiednio „A0” i „D0”.Wszystkie wewnętrzne ścieżki danych i ALU mają szerokość 16 bitów.

Procesor może być wstrzymany z trójstanową magistralą adresową dla zewnętrznego bezpośredniego dostępu do pamięci (DMA). Dostęp do pamięci ma zawsze szerokość 16 bitów, przy czym procesor automatycznie wykonuje operacje odczytu przed zapisem dla dostępu o szerokości bajtów.

System przerwań sprzętowych obsługuje 4-bitowe wejście priorytetu przerwania, które musiało być wyższe niż poziom priorytetu przechowywany w rejestrze stanu (bity 12-15), aby żądanie przerwania zostało obsłużone. Ponadto wejście /LOAD zapewnia niemaskowalną funkcję przerwania z dedykowanym wektorem.

Jednostka centralna TMS9900 zawiera również 16-bitowy rejestr przesuwny ("CRU") zaprojektowany do współpracy z zewnętrznymi rejestrami przesuwnymi, z dedykowanymi instrukcjami obsługującymi dostęp do pól o szerokości 1-16 bitów z łącznej liczby 4096 bitów adresowalnych.

Równoległe urządzenia peryferyjne można podłączyć w sposób mapowany w pamięci do zwykłego adresu i magistrali danych.

Aplikacje

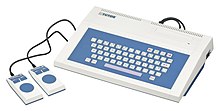

TMS9900 był używany w komputerach domowych TI-99/4 i TI-99/4A . Niestety, aby obniżyć koszty produkcji, firma TI zdecydowała się na użycie w tych systemach zaledwie 128 16-bitowych słów szybkiej pamięci RAM, do której TMS9900 miał bezpośredni dostęp. Reszta pamięci to 16 kB 8-bitowej pamięci DRAM, która była dostępna tylko pośrednio przez kontroler wyświetlania wideo, co obniżało wydajność TI-99/4.

TI opracowało serię modułów komputerowych TM990, w tym procesor, pamięć, I/O, które po podłączeniu do ramki karty mogą tworzyć 16-bitowy minikomputer. Były one zwykle używane do kontroli procesu. Trenażer mikroprocesorowy został wydany w postaci TM990/189.

Rozwój produktów rodziny TMS9900

Drugą generacją mikroprocesorów z rodziny TMS9900 był TMS9995, który zapewniał „funkcjonalną wydajność przy prędkościach 3 razy szybszych niż jakikolwiek poprzedni procesor z rodziny 9900”, głównie dzięki zastosowaniu technologii wstępnego pobierania instrukcji. Na arenie komputerów domowych TMS9995 znalazł zastosowanie tylko w Tomy Tutor , ezoterycznej aktualizacji TI99-4/A o nazwie Geneve 9640 i projekcie wydrukowanym w Electronics Today : Powertran Cortex. Planowano jej zastosowanie w systemach komputerowych TI-99/2 i TI-99/8, ale nie przekroczyła stadium prototypu.

Firma TI opracowała później wydajniejszą rodzinę mikroprocesorów TMS99000, która została wykorzystana jako procesor w minikomputerze 990/10A w celu obniżenia kosztów. Niestety, zanim 990/10A trafił na rynek, koniec ery minikomputerów był już w zasięgu wzroku.

Rodzina TMS99000 obejmuje dwa mikroprocesory, TMS99105A i TMS99110A, które są identyczne, z wyjątkiem wbudowanej pamięci ROM magazynu makro (pamięć magazynu makro zawiera dodatkowe funkcje lub instrukcje poprzez procedury emulacji zapisane w standardowym kodzie maszynowym). Pamięć makr ROM na chipie w mikroprocesorze TMS99110A zawiera instrukcje zmiennoprzecinkowe, które są dostępne jako część zestawu instrukcji języka maszynowego, podczas gdy TMS99105A nie zawiera pamięci makr ROM. Trzeci członek rodziny TMS99000, TMS99120, został ogłoszony, ale prawdopodobnie nigdy nie był produkowany komercyjnie. Wbudowany w chip ROM Macrostore w TMS99120 zawiera procedury obsługi w czasie wykonywania dla języka wysokiego poziomu PASCAL.

Zestaw instrukcji dla rodziny TMS99000 jest nadzbiorem TMS9995 i TMS9900, z kompatybilnością kodu obiektowego. Dodatkowe instrukcje obejmują instrukcje mnożenia i dzielenia ze znakiem; przesunięcie długich słów, dodawanie i odejmowanie; rejestr stanu obciążenia, wskaźnik miejsca pracy obciążenia, operacje na stosie, obsługa wieloprocesorów, manipulacja bitami. Członkowie rodziny mogą natychmiast uzyskać dostęp do 256 KB pamięci i mogą używać mapowania pamięci TIM99610 do adresowania do 16 MB. Architektura zawiera wiele innych udoskonaleń w porównaniu z TMS9900 i TMS9995.

Warianty

| Model | Opis |

|---|---|

| TI990/9 | Wczesny wieloukładowy procesor do systemów minikomputerowych, 1974 |

| TI990/10 | Implementacja wielochipowa dla systemów minikomputerowych, 1975 |

| TI990/12 | Implementacja wielochipowa, szybsza niż 990/10 |

| TMS9900 | Implementacja jednoukładowa, 1976, stosowana w komputerze TI-99/4(A) |

| TMS9940 | Mikrokontroler z 2KB ROM, 128B RAM, dekrementator, magistrala CRU, 1979 |

| TMS9980 TMS9981 |

8-bitowe wersje TMS9900 |

| TMS9985 | TMS9940 z 8KB ROM, 256B RAM i 8-bitową zewnętrzną magistralą, 1978 (nigdy nie wydany) |

| TMS9989 | Ulepszony 9980, używany w sprzęcie wojskowym |

| TMS9995 | Ulepszony podobny do TMS9985, bez pamięci ROM. Używany w prototypach TI-99/2 i TI-99/8, Tomy Tutor i komputerze Geneve |

| TMS99105 | Podstawowy członek rodziny mikroprocesorów TMS99000 |

| TMS99110 | Mikroprocesor rodziny TMS99000 z instrukcjami zmiennoprzecinkowymi zaprogramowanymi w wbudowanej pamięci ROM Macrostore |

| TMS99120 | Mikroprocesor z rodziny TMS99000 z procedurami obsługi w czasie wykonywania dla języka wysokiego poziomu PASCAL, wstępnie zaprogramowanymi w wbudowanej pamięci ROM Macrostore (mikroprocesor został ogłoszony, ale być może nigdy nie był produkowany komercyjnie) |

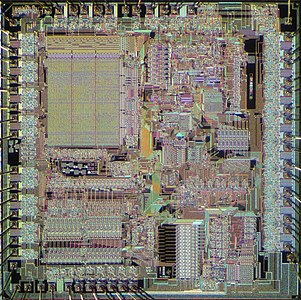

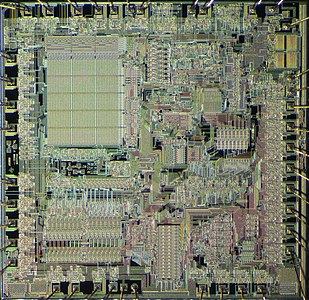

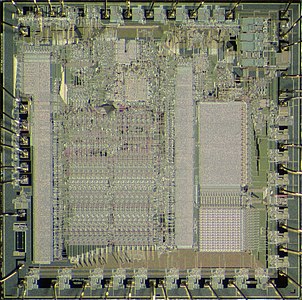

- Umierać zdjęcia

Bibliografia

Zewnętrzne linki

- Instrukcje TMS9900 i referencje od Bitsavers