Intel 8008 -Intel 8008

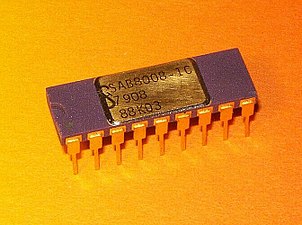

Wariant procesora Intel C8008-1 z fioletową ceramiką, pozłacaną metalową pokrywą i stykami.

| |

| Informacje ogólne | |

|---|---|

| Wystrzelony | połowa 1972 r |

| Przerwane | 1983 |

| Zaprojektowany przez | Korporacja Terminali Komputerowych (CTC) |

| Wspólni producenci | |

| Wydajność | |

| Maks. Częstotliwość taktowania procesora | 200 kHz do 800 kHz |

| Szerokość danych | 8 bitów |

| Szerokość adresu | 14 bitów |

| Architektura i klasyfikacja | |

| Aplikacja | Terminale komputerowe , kalkulatory , rozlewarki, roboty przemysłowe ASEA z lat 70. (IRB 6), proste komputery itp. |

| Węzeł technologiczny | 10 µm |

| Zestaw instrukcji | 8008 |

| Specyfikacje fizyczne | |

| Tranzystory | |

| pakiet(y) | |

| Gniazdo(a) | |

| Historia | |

| Następca | Intel 8080 |

| Stan wsparcia | |

| Nieobsługiwany | |

Intel 8008 („ osiem tysięcy osiem ” lub „ osiemdziesiąt osiem ”) to wczesny mikroprocesor zorientowany na bajty, zaprojektowany przez Computer Terminal Corporation (CTC), wdrożony i wyprodukowany przez firmę Intel i wprowadzony na rynek w kwietniu 1972 roku. 8-bitowy procesor z zewnętrzną 14-bitową magistralą adresową, która może adresować 16 KB pamięci. Pierwotnie znany jako 1201 , chip został zamówiony przez Computer Terminal Corporation (CTC) w celu zaimplementowania zestawu instrukcji ich projektu dla programowalnego terminala Datapoint 2200 . Ponieważ chip był opóźniony i nie spełniał celów wydajnościowych CTC, 2200 zamiast tego używał własnego procesora CTC opartego na TTL . Umowa zezwoliła Intelowi na sprzedaż chipa innym klientom po tym, jak Seiko wyraziło zainteresowanie wykorzystaniem go w kalkulatorze .

Historia

CTC powstało w San Antonio w 1968 roku pod kierownictwem Austina O. „Gusa” Roche'a i Phila Raya, inżynierów NASA . W szczególności firma Roche była zainteresowana przede wszystkim produkcją komputera stacjonarnego. Jednak biorąc pod uwagę niedojrzałość rynku, biznesplan firmy wspominał tylko o zamienniku Teletype Model 33 ASR, który był dostarczany jako Datapoint 3300 . Obudowa została celowo zaprojektowana tak, aby mieściła się w tej samej przestrzeni, co maszyna do pisania IBM Selectric i wykorzystywała ekran wideo o takim samym współczynniku proporcji jak karta dziurkowana IBM . Chociaż model 3300 odniósł sukces komercyjny, miał ciągłe problemy z przegrzewaniem się z powodu ilości obwodów upakowanych na tak małej przestrzeni.

Aby rozwiązać problemy z ogrzewaniem i innymi problemami, rozpoczęto przeprojektowanie, w którym część procesora wewnętrznych obwodów została ponownie wdrożona na jednym chipie. Poszukując firmy, która byłaby w stanie wyprodukować ich projekt chipa, Roche zwrócił się do Intela, który wówczas był przede wszystkim dostawcą układów pamięci. Roche spotkał się z Bobem Noycem , który wyraził zaniepokojenie tą koncepcją; John Frassanito wspomina, że „Noyce powiedział, że to intrygujący pomysł i że Intel mógłby to zrobić, ale byłoby to głupie posunięcie. Powiedział, że jeśli masz chip komputerowy, możesz sprzedać tylko jeden chip na komputer, podczas gdy z pamięcią , możesz sprzedać setki żetonów na komputer”. Innym poważnym problemem było to, że istniejąca baza klientów Intela kupowała układy pamięci do użytku z własnymi projektami procesorów; gdyby Intel wprowadził własny procesor, mógłby być postrzegany jako konkurent, a ich klienci mogliby szukać pamięci gdzie indziej. Niemniej jednak Noyce zgodził się na kontrakt rozwojowy o wartości 50 000 USD na początku 1970 r. Firma Texas Instruments (TI) została również wprowadzona jako drugi dostawca.

TI był w stanie wykonać próbki 1201 na podstawie rysunków Intela, ale okazały się one błędne i zostały odrzucone. Własne wersje Intela były opóźnione. CTC zdecydowało się ponownie zaimplementować nową wersję terminala przy użyciu dyskretnego TTL zamiast czekać na jednoukładowy procesor. Nowy system został wydany jako Datapoint 2200 wiosną 1970 r., A ich pierwsza sprzedaż firmie General Mills 25 maja 1970 r. CTC wstrzymało rozwój 1201 po wypuszczeniu 2200, ponieważ nie był już potrzebny. Sześć miesięcy później Seiko zwróciła się do Intela, wyrażając zainteresowanie użyciem 1201 w kalkulatorze naukowym, prawdopodobnie po zobaczeniu sukcesu prostszego Intel 4004 używanego przez Busicom w ich kalkulatorach biznesowych. Nastąpił niewielki przeprojektowanie, pod kierownictwem Federico Faggina , projektanta 4004, obecnie lidera projektu 1201, rozszerzając konstrukcję z 16-pinowej na 18-pinową, a nowy 1201 został dostarczony do CTC pod koniec 1971 roku .

W tym momencie CTC po raz kolejny ruszyło dalej, tym razem do Datapoint 2200 II , który był szybszy. 1201 nie był już wystarczająco mocny dla nowego modelu. CTC głosowało za zakończeniem swojego zaangażowania w 1201, pozostawiając własność intelektualną projektu firmie Intel zamiast płacić kontrakt o wartości 50 000 USD. Intel zmienił jego nazwę na 8008 i umieścił go w swoim katalogu w kwietniu 1972 roku w cenie 120 USD. Ta zmiana nazwy próbowała zniwelować sukces chipa 4004, przedstawiając 8008 jako po prostu port 4 do 8, ale 8008 nie jest oparty na 4004. 8008 odniósł sukces komercyjny. Następnie pojawił się Intel 8080 , a następnie niezwykle udana rodzina Intel x86 .

Jednym z pierwszych zespołów, które zbudowały kompletny system wokół 8008, był zespół Billa Pentza z California State University w Sacramento . Sac State 8008 był prawdopodobnie pierwszym prawdziwym mikrokomputerem z dyskowym systemem operacyjnym zbudowanym z asemblera IBM Basic w PROM, a wszystko to sterowało kolorowym wyświetlaczem, dyskiem twardym, klawiaturą, modemem, czytnikiem taśm audio/papierowych i drukarką. Projekt rozpoczął się wiosną 1972 roku, a rok później, przy kluczowej pomocy firmy Tektronix , system był w pełni funkcjonalny. Bill pomagał Intelowi przy zestawie MCS-8 i dostarczył kluczowych informacji do zestawu instrukcji Intel 8080 , co pomogło uczynić go użytecznym dla przemysłu i hobbystów.

W Wielkiej Brytanii zespół SE Laboratories Engineering (EMI) kierowany przez Toma Spinka w 1972 roku zbudował mikrokomputer oparty na przedpremierowej próbce 8008. Joe Hardman rozszerzył chip o zewnętrzny stos. To, między innymi, zapewniło mu zapisywanie i przywracanie po awarii zasilania. Joe opracował również bezpośrednią drukarkę sitodrukową. System operacyjny został napisany przy użyciu metaasemblera opracowanego przez L. Crawforda i J. Parnella dla Digital Equipment Corporation PDP-11 . System operacyjny został spalony na PROM. Był sterowany przerwaniami, kolejkowany i oparty na stałym rozmiarze strony dla programów i danych. Prototyp operacyjny został przygotowany dla kierownictwa, które zdecydowało się nie kontynuować projektu.

8008 był procesorem dla pierwszych komercyjnych komputerów osobistych niebędących kalkulatorami (z wyłączeniem samego Datapoint 2200): amerykańskiego zestawu SCELBI oraz gotowego francuskiego Micral N i kanadyjskiego MCM / 70 . Był to również mikroprocesor sterujący dla kilku pierwszych modeli terminali komputerowych z rodziny 2640 firmy Hewlett-Packard.

Intel zaoferował symulator zestawu instrukcji dla 8008 o nazwie INTERP / 8. Został napisany w języku FORTRAN .

Projekt

| 1 3 | 1 2 | 1 1 | 1 0 | 0 9 | 0 8 | 0 7 | 0 6 | 0 5 | 0 4 | 0 3 | 0 2 | 0 1 | 0 0 | (pozycja bitu) |

| Rejestry główne | ||||||||||||||

| A | Akumulator _ | |||||||||||||

| B | Rejestr B | |||||||||||||

| C | Rejestr C | |||||||||||||

| D | Rejestr D | |||||||||||||

| mi | Rejestr E | |||||||||||||

| H | Rejestr H (pośredni) | |||||||||||||

| Ł | Rejestr L (pośredni) | |||||||||||||

| Licznik programu | ||||||||||||||

| komputer | Licznik programów _ _ | |||||||||||||

| Stos wywołań adresów przesuwanych w dół | ||||||||||||||

| JAK | Poziom połączenia 1 | |||||||||||||

| JAK | Poziom połączenia 2 | |||||||||||||

| JAK | Poziom połączenia 3 | |||||||||||||

| JAK | Poziom połączenia 4 | |||||||||||||

| JAK | Poziom połączenia 5 | |||||||||||||

| JAK | Poziom połączenia 6 | |||||||||||||

| JAK | Poziom połączenia 7 | |||||||||||||

| Flagi | ||||||||||||||

| C | P | Z | S | Flagi | ||||||||||

8008 został zaimplementowany w logice PMOS z bramką krzemową w trybie wzmocnienia 10 μm . Początkowe wersje mogły pracować z częstotliwościami taktowania do 0,5 MHz. Zostało to później zwiększone w 8008-1 do określonego maksimum 0,8 MHz. Instrukcje przyjmują od 5 do 11 stanów T, gdzie każdy stan T to 2 cykle zegara. Rejestr-rejestr obciążenia i operacje ALU zajmują 5T (20 μs przy 0,5 MHz), rejestr-pamięć 8T (32 μs), podczas gdy wywołania i skoki (po wykonaniu) zajmują 11 stanów T (44 μs). 8008 jest nieco wolniejszy pod względem liczby instrukcji na sekundę (36 000 do 80 000 przy 0,8 MHz) niż 4-bitowe Intel 4004 i Intel 4040 . ale ponieważ 8008 przetwarza dane 8 bitów na raz i może uzyskać dostęp do znacznie większej ilości pamięci RAM, w większości aplikacji ma znaczną przewagę prędkości nad tymi procesorami. 8008 ma 3500 tranzystorów .

Chip (ograniczony przez 18-pinowy DIP ) ma pojedynczą 8-bitową magistralę i wymaga znacznej ilości zewnętrznej logiki pomocniczej. Na przykład adres 14-bitowy, który może uzyskać dostęp do „16 K × 8 bitów pamięci”, musi zostać zablokowany przez część tej logiki w rejestrze adresu pamięci zewnętrznej (MAR). 8008 może uzyskać dostęp do 8 portów wejściowych i 24 portów wyjściowych.

W przypadku kontrolera i terminala CRT jest to akceptowalna konstrukcja, ale jest raczej nieporęczna w większości innych zadań, przynajmniej w porównaniu z następną generacją mikroprocesorów. Opierało się na nim kilka wczesnych projektów komputerów, ale większość zamiast tego używała późniejszego i znacznie ulepszonego Intel 8080 .

Powiązane projekty procesorów

Kolejny 40-pinowy NMOS Intel 8080 rozszerzył rejestry i zestaw instrukcji 8008 oraz implementuje bardziej wydajny interfejs magistrali zewnętrznej (wykorzystując 22 dodatkowe piny). Pomimo bliskiego związku architektonicznego, 8080 nie był kompatybilny binarnie z 8008, więc program 8008 nie działałby na 8080. Jednak ponieważ Intel używał wówczas dwóch różnych składni asemblera, 8080 mógł być używany w 8008 kompatybilność wsteczna języka asemblera.

Intel 8085 to elektrycznie zmodernizowana wersja 8080, która wykorzystuje tranzystory w trybie wyczerpania , a także dodaje dwie nowe instrukcje.

Intel 8086 , oryginalny procesor x86, jest nieścisłym rozszerzeniem 8080, więc luźno przypomina również oryginalny projekt Datapoint 2200. Prawie każda instrukcja Datapoint 2200 i 8008 ma odpowiednik nie tylko w zestawie instrukcji 8080, 8085 i Z80 , ale także w zestawie instrukcji nowoczesnych procesorów x86 (chociaż kodowanie instrukcji jest różne).

Cechy

Architektura 8008 obejmuje następujące funkcje:

- Siedem 8-bitowych rejestrów „scratchpad”: główny akumulator (A) i sześć innych rejestrów (B, C, D, E, H i L).

- 14-bitowy licznik programów (PC).

- Siedmiopoziomowy stos wywołań adresów przesuwanych w dół . W rzeczywistości używanych jest osiem rejestrów, z których najwyższym jest rejestr PC.

- Cztery flagi stanu kodu warunku: przeniesienie (C), parzystość (P), zero (Z) i znak (S).

- Pośredni dostęp do pamięci przy użyciu rejestrów H i L (HL) jako 14-bitowego wskaźnika danych (dwa górne bity są ignorowane).

Przykładowy kod

Poniższy kod źródłowy zestawu 8008 dotyczy podprogramu o nazwie MEMCPY, który kopiuje blok bajtów danych o danym rozmiarze z jednego miejsca do drugiego.

001700 000

001701 000

001702 000

001703 000

001704 000

001705 000

002000 066 304

002002 056 003

002004 327

002005 060

002006 317

002007 302

002010 261

002011 053

002012 302

002013 024 001

002015 320

002016 301

002017 034 000

002021 310

002022 066 300

002024 056 003

002026 302

002027 207

002030 340

002031 060

002032 301

002033 217

002034 350

002035 364

002036 337

002037 066 302

002041 056 003

002043 302

002044 207

002045 340

002046 060

002047 301

002050 217

002051 350

002035 364

002052 373

002053 104 007 004

002056

|

; MEMCPY --

; Copy a block of memory from one location to another.

;

; Entry parameters

; SRC: 14-bit address of source data block

; DST: 14-bit address of target data block

; CNT: 14-bit count of bytes to copy

ORG 1700Q ;Data at 001700q

SRC DFB 0 ;SRC, low byte

DFB 0 ; high byte

DST DFB 0 ;DST, low byte

DFB 0 ; high byte

CNT DFB 0 ;CNT, low byte

DFB 0 ; high byte

ORG 2000Q ;Code at 002000q

MEMCPY LLI CNT+0 ;HL = addr(CNT)

LHI CNT+1

LCM ;BC = CNT

INL

LBM

LOOP LAC ;If BC = 0,

ORB

RTZ ;Return

DECCNT LAC ;BC = BC - 1

SUI 1

LCA

LAB

SBI 0

LBA

GETSRC LLI SRC+0 ;HL = addr(SRC)

LHI SRC+1

LAC ;HL = SRC + BC

ADM ;E = C + (HL)

LEA ;(lower sum)

INL ;point to upper SRC

LAB

ACM ;H = B + (HL) + CY

LHA ;(upper sum)

LLE ;L = E

LDM ;Load D from (HL)

GETDST LLI DST+0 ;HL = addr(DST)

LHI DST+1

LAC ;HL = DST + BC

ADM ;ADD code same as above

LEA

INL

LAB

ACM

LHA

LLE

LMD ;Store D to (HL)

JMP LOOP ;Repeat the loop

END

|

W powyższym kodzie wszystkie wartości są podane w systemie ósemkowym. Lokalizacje SRC, DSTi CNTsą 16-bitowymi parametrami podprogramu o nazwie MEMCPY. W rzeczywistości używanych jest tylko 14 bitów wartości, ponieważ procesor ma tylko 14-bitową adresowalną przestrzeń pamięci. Wartości są przechowywane w formacie little-endian , chociaż jest to wybór arbitralny, ponieważ procesor nie jest w stanie odczytywać ani zapisywać więcej niż jednego bajtu w pamięci naraz. Ponieważ nie ma instrukcji ładowania rejestru bezpośrednio z podanego adresu pamięci, para rejestrów HL musi najpierw zostać załadowana adresem, a następnie rejestr docelowy może zostać załadowany z operandu M, co jest ładowaniem pośrednim z lokalizacji pamięci w parze rejestrów HL. Para rejestrów BC jest ładowana wartością CNTparametru i zmniejszana na końcu pętli, aż osiągnie zero. Należy zauważyć, że większość używanych instrukcji zajmuje pojedynczy 8-bitowy kod operacji.

Projektanci

- CTC ( zbiór instrukcji i architektura ): Victor Poor i Harry Pyle .

-

Intel ( Implementacja w krzemie ):

- Ted Hoff , Stan Mazor i Larry Potter (główny naukowiec IBM) zaproponowali jednoukładową implementację architektury CTC, wykorzystującą pamięć RAM-rejestrową zamiast pamięci rejestrowej przesuwnej, a także dodali kilka instrukcji i obsługę przerwań. Projekt chipa 8008 (pierwotnie nazywany 1201) rozpoczął się przed rozwojem 4004. Hoff i Mazor nie mogli jednak opracować i nie opracowali „konstrukcji krzemowej”, ponieważ nie byli ani projektantami chipów, ani twórcami procesów, a ponadto niezbędną metodologię i obwody projektowe oparte na bramkach krzemowych, opracowywane przez Federico Faggina dla 4004, nie były jeszcze dostępne.

- Federico Faggin , po ukończeniu projektu 4004, stał się liderem projektu od stycznia 1971 roku do jego pomyślnego zakończenia w kwietniu 1972 roku, po tym jak został zawieszony – z powodu braku postępów – na około siedem miesięcy.

- Hal Feeney , inżynier projektu, wykonał szczegółowy projekt logiki, projekt obwodów i układ fizyczny pod nadzorem Faggina, stosując tę samą metodologię projektowania, którą Faggin pierwotnie opracował dla mikroprocesora Intel 4004, i wykorzystując podstawowe obwody, które opracował dla 4004. Połączone logo „HF” zostało wytrawione na chipie mniej więcej w połowie odległości między podkładkami łączącymi D5 i D6.

Drugie źródła

- Drugie źródła Intel 8008

MicroSystems International (MIL) MF8008

Siemensa SAB8008

Zobacz też

- Mark-8 i SCELBI , zestawy komputerowe oparte na 8008

- MCM/70 i Micral , pionierskie mikrokomputery

- PL/M , pierwszy język programowania ukierunkowany na mikroprocesor, Intel 8008, opracowany przez Gary'ego Kildalla

Bibliografia

Linki zewnętrzne

- Instrukcja obsługi MCS-8 z kartą katalogową 8008 (1972)

- Drewno, Lamont (8 sierpnia 2008). „Zapomniana historia komputerów PC: prawdziwe pochodzenie komputera osobistego” . Świat komputerów .

- Strona wsparcia Intel 8008 nieoficjalna

- Strona DigiBarn Computer Museum na temat maszyny Billa Pentza Sacramento State, pełnego mikrokomputera zbudowanego wokół 8008

-

Martin, Donald P. (1974). Projektowanie mikrokomputerów . Badania Marcina .

- — (1976). Projekt mikrokomputera (wyd. 2). Badania Marcina . OCLC 911808003 .

- Runyan, Grant (kwiecień 1977). „Teraz — BASIC dla 8008 — nawet!” . Magazyn Kilobaud : 116–8.

- „Tłumacz języka BASIC dla mikroprocesora Intel 8008” . Uniwersytet Illinois. 1974.

- 8008 Karta referencyjna języka asemblera

-

Shirriff, Ken (grudzień 2016). „Die zdjęcia i analiza rewolucyjnego mikroprocesora 8008, 45 lat” .

- — (luty 2017 r.). „Inżynieria wsteczna zaskakująco zaawansowanej jednostki ALU mikroprocesora 8008” .

- — (październik 2020). „Jak ładowanie początkowe umożliwiło historyczny procesor Intel 8008” .

- — (listopad 2020). „Inżynieria wsteczna obwodu typu carry-lookahead w procesorze Intel 8008” .