Rozciąganie IBM 7030 — IBM 7030 Stretch

| Rozciąganie IBM | |

|---|---|

Konsola serwisowa IBM 7030 w Musée des Arts et Métiers w Paryżu

| |

| Projekt | |

| Producent | IBM |

| Projektant | gen Amdahl |

| Data wydania | maj 1961 |

| Sprzedane jednostki | 9 |

| Cena | 7 780 000 USD (równowartość 67 380 000 USD w 2020 r.) |

| Obudowa | |

| Waga | 70 000 funtów (35 ton amerykańskich; 32 t) |

| Moc | 100 kW przy 110 V |

| System | |

| System operacyjny | MCP |

| procesor | 64-bitowy procesor |

| Pamięć | 2048 kilobajtów (262144 x 64 bity) |

| MIPS | 1.2 MIPS |

IBM 7030 , znany także jako Stretch był IBM pierwszy jest tranzystorowy supercomputer . Był to najszybszy komputer na świecie od 1961 roku, aż do uruchomienia pierwszego CDC 6600 w 1964 roku.

Pierwotnie zaprojektowany, aby spełnić wymagania sformułowane przez Edwarda Tellera w Lawrence Livermore National Laboratory , pierwszy egzemplarz dostarczono do Los Alamos National Laboratory w 1961 roku, a druga dostosowana wersja, IBM 7950 Harvest , do Narodowej Agencji Bezpieczeństwa w 1962 roku. w tym broni atomowej Research Establishment w Aldermaston , Anglia była mocno wykorzystywane przez badaczy tam i na ære Harwell , ale dopiero po rozwoju S2 Fortran Compiler, który był pierwszy i dodaj dynamiczne tablice , a który później został przeniesiony do Ferrantiego Atlas of Atlas Computer Laboratory w Chilton.

7030 był znacznie wolniejszy niż oczekiwano i nie osiągnął swoich agresywnych celów wydajności. IBM został zmuszony do obniżenia ceny z 13,5 mln do zaledwie 7,78 mln USD i wycofał 7030 ze sprzedaży klientom poza tymi, którzy już wynegocjowali kontrakty. Magazyn PC World nazwał Stretch jedną z największych porażek w zarządzaniu projektami w historii IT .

W IBM bycie przyćmionym przez mniejszą firmę Control Data Corporation wydawało się trudne do zaakceptowania. Kierownik projektu, Stephen W. Dunwell, był początkowo kozłem ofiarnym za swoją rolę w „porażce”, ale gdy sukces IBM System/360 stał się oczywisty, otrzymał oficjalne przeprosiny, a w 1966 roku został mianowany przez IBM. Kolega .

Mimo, że Stretch nie osiągnął własnych celów wydajnościowych, posłużył jako podstawa wielu funkcji projektowych udanego IBM System/360, który został dostarczony w 1964 roku.

Historia rozwoju

Na początku 1955 roku dr Edward Teller z Laboratorium Radiacyjnego Uniwersytetu Kalifornijskiego chciał nowego naukowego systemu obliczeniowego do trójwymiarowych obliczeń hydrodynamicznych . Poproszono IBM i UNIVAC o nowy system, który miał się nazywać Livermore Automatic Reaction Calculator lub LARC . Według dyrektora IBM, Cuthberta Hurda , taki system kosztowałby około 2,5 miliona dolarów i działałby z prędkością od jednego do dwóch MIPS . Dostawa miała nastąpić od dwóch do trzech lat po podpisaniu umowy.

W IBM mały zespół w Poughkeepsie, w tym John Griffith i Gene Amdahl, pracował nad propozycją projektu. Zaraz po tym, jak skończyli i mieli przedstawić propozycję, Ralph Palmer zatrzymał ich i powiedział: „To pomyłka”. Proponowana konstrukcja zostałaby zbudowana z wykorzystaniem tranzystorów stykowych lub tranzystorów z barierą powierzchniową , które prawdopodobnie zostaną wkrótce prześcignięte przez nowo wynaleziony tranzystor dyfuzyjny .

IBM wrócił do Livermore i oświadczył, że wycofuje się z kontraktu, a zamiast tego zaproponował dramatycznie lepszy system: „Nie zbudujemy dla ciebie tej maszyny; chcemy zbudować coś lepszego! Nie wiemy dokładnie, co to zajmie ale myślimy, że będzie to kolejny milion dolarów i kolejny rok, i nie wiemy, jak szybko będzie działać, ale chcielibyśmy strzelać z dziesięcioma milionami instrukcji na sekundę”. Livermore nie był pod wrażeniem iw maju 1955 roku ogłosili, że UNIVAC wygrał kontrakt LARC , obecnie nazywany Livermore Automatic Research Computer . LARC został ostatecznie dostarczony w czerwcu 1960 roku.

We wrześniu 1955 roku, obawiając się, że Los Alamos National Laboratory może również zamówić LARC, IBM przedstawił wstępną propozycję wysokowydajnego komputera binarnego, opartego na ulepszonej wersji projektu, który odrzucił Livermore, którą otrzymał z zainteresowaniem. W styczniu 1956 roku formalnie rozpoczęto projekt Stretch. W listopadzie 1956 r. IBM wygrał kontrakt z agresywnym celem w zakresie wydajności „przynajmniej 100 razy większa od IBM 704 ” (tj. 4 MIPS). Dostawa była przewidziana na 1960.

Podczas projektowania okazało się, że konieczne jest zmniejszenie częstotliwości taktowania, co jasno pokazuje, że Stretch nie był w stanie osiągnąć swoich agresywnych celów wydajnościowych, ale szacowana wydajność wahała się od 60 do 100 razy w porównaniu z IBM 704. W 1960 r. ustalono cenę 13,5 mln USD na IBM 7030. W 1961 r. rzeczywiste testy porównawcze wskazywały, że wydajność IBM 7030 była tylko około 30 razy większa niż IBM 704 (tj. 1,2 MIPS), co spowodowało znaczne zakłopotanie dla IBM. W maju 1961 Tom Watson ogłosił obniżkę cen wszystkich 7030-tych będących przedmiotem negocjacji do 7,78 miliona dolarów i natychmiastowe wycofanie produktu z dalszej sprzedaży.

Jego czas dodawania zmiennoprzecinkowego wynosi 1,38–1,50 mikrosekund , czas mnożenia to 2,48–2,70 mikrosekund, a czas dzielenia to 9,00–9,90 mikrosekund.

Wpływ techniczny

Chociaż IBM 7030 nie był uważany za udany, zrodził wiele technologii zastosowanych w przyszłych maszynach, które odniosły duży sukces. Standardowy System modułowy tranzystor logika była podstawą dla IBM 7090 linii komputerów naukowe, IBM 7070 i 7080 komputerów biznesowych, IBM 7040 i IBM 1400 linii, a IBM 1620 mały komputer naukowe; 7030 używało około 170 000 tranzystorów. Jednostki IBM 7302 Model I Core Storage były również używane w IBM 7090, IBM 7070 i IBM 7080. Wieloprogramowanie , ochrona pamięci, uogólnione przerwania, ośmiobitowy bajt dla I/O zostały później włączone do IBM System/360 linia komputerów, a także większość późniejszych jednostek centralnych (CPU).

Stephen Dunwell, kierownik projektu, który stał się kozłem ofiarnym, gdy Stretch zawiódł komercyjnie, zauważył wkrótce po fenomenalnie udanym uruchomieniu System/360 w 1964 roku, że większość jego podstawowych koncepcji zapoczątkował Stretch. Do roku 1966 otrzymał przeprosiny i został członkiem IBM Fellow, co niosło za sobą środki i autorytet do prowadzenia poszukiwanych badań.

Rurociąg instrukcja , prefetch i dekodowania i przeplatanie pamięci zostały wykorzystane w późniejszym superkomputera wzorów, takich jak IBM System / 360 modeli 91 , 95 i 195 , a IBM 3090 serii, jak i innych producentów komputerów. Od 2021 r. techniki te są nadal stosowane w większości zaawansowanych mikroprocesorów, począwszy od generacji z lat 90., która obejmowała Intel Pentium i Motorola/IBM PowerPC , a także w wielu wbudowanych mikroprocesorach i mikrokontrolerach różnych producentów.

Implementacja sprzętowa

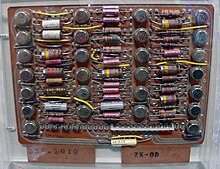

Procesor 7030 wykorzystuje logikę sprzężoną z emiterem (pierwotnie nazywaną logiką sterowania prądem ) na 18 typach kart Standard Modular System (SMS). Wykorzystuje 4025 kart podwójnych (jak pokazano) i 18 747 kart pojedynczych, mieszczących 169 100 tranzystorów, co wymaga łącznej mocy 21 kW. Wykorzystuje on szybkie, germanowe tranzystory dryfowe NPN i PNP , o częstotliwości odcięcia powyżej 100 MHz i wykorzystujące ~50 mW każdy. Niektóre obwody trzeciego poziomu wykorzystują trzeci poziom napięcia. Każdy poziom logiczny ma opóźnienie około 20 ns. Aby zwiększyć prędkość w krytycznych obszarach, stosuje się logikę wtórnika emitera w celu zmniejszenia opóźnienia do około 10 ns.

Wykorzystuje tę samą pamięć rdzeniową, co IBM 7090 .

Instalacje

- Laboratorium Naukowe Los Alamos (LASL) w kwietniu 1961, przyjęte w maju 1961 i używane do 21 czerwca 1971.

- Lawrence Livermore National Laboratory , Livermore, Kalifornia, dostarczone w listopadzie 1961.

- Amerykańska Agencja Bezpieczeństwa Narodowego w lutym 1962 r. jako główny procesor systemu IBM 7950 Harvest , używanego do 1976 r., kiedy system taśm IBM 7955 Tractor napotkał problemy z powodu zużytych krzywek, których nie można było wymienić.

- Zakład Broni Atomowej , Aldermaston , Anglia, dostarczony w lutym 1962 r.

- US Weather Bureau Washington DC, dostarczone w czerwcu/lipcu 1962.

- MITER Corporation , dostarczony w grudniu 1962 r. i używany do sierpnia 1971 r. Wiosną 1972 r. został sprzedany na Uniwersytecie Brighama Younga , gdzie był używany przez wydział fizyki do momentu złomowania w 1982 r.

- US Navy Dahlgren Naval Proving Ground , dostarczony we wrześniu/październiku 1962.

- Commissariat à l'énergie atomique , Francja, wygłoszony w listopadzie 1963 r.

- IBM.

IBM 7030 Lawrence Livermore Laboratory (z wyjątkiem pamięci podstawowej ) i fragmenty IBM 7030 firmy MITER Corporation/Brigham Young University znajdują się obecnie w kolekcji Computer History Museum w Mountain View w Kalifornii .

Architektura

Formaty danych

- Liczby stałoprzecinkowe mają zmienną długość, są przechowywane w postaci binarnej (od 1 do 64 bitów) lub dziesiętnej (od 1 do 16 cyfr) w formacie bez znaku lub w formacie znak/wielkość . W formacie dziesiętnym cyfry są bajtami o zmiennej długości (4 do 8 bitów).

- Liczby zmiennoprzecinkowe mają 1-bitową flagę wykładnika, 10-bitową wykładnik, 1-bitowy znak wykładnika, 48-bitową wielkość i 4-bitowy bajt znaku w formacie znak/wielkość.

- Znaki alfanumeryczne mają zmienną długość i mogą używać dowolnego kodu znaków o długości 8 bitów lub mniej.

- Bajty mają zmienną długość (od 1 do 8 bitów).

Format instrukcji

Instrukcje są 32-bitowe lub 64-bitowe.

Rejestry

Rejestry nakładają się na pierwsze 32 adresy pamięci, jak pokazano.

| ! Adres | Mnemoniczny | Zarejestrować | Przechowywane w: |

|---|---|---|---|

| 0 | $Z | 64-bitowe zero: zawsze czytane jako zero, nie może być zmienione przez zapisy | Główne miejsce do przechowywania rdzeni |

| 1 | $IT | timer interwałowy (bity 0..18): zmniejszany o 1024 Hz, powtarza się co około 8,5 minuty, przy zerze włącza „wskaźnik sygnału czasu” w rejestrze wskaźnika | Pamięć rdzenia indeksu |

| $TC | 36-bitowy zegar czasu (bity 28..63): liczba taktów 1024 Hz, przyrost bitów 38..63 raz na sekundę, cykle co ~777 dni. | ||

| 2 | $IA | 18-bitowy adres przerwania | Główne miejsce do przechowywania rdzeni |

| 3 | $UB | 18-bitowy adres górnej granicy (bity 0-17) | Rejestr tranzystorów |

| $LB | 18-bitowy adres dolnej granicy (bity 32-49) | ||

| 1-bitowa kontrola granic (bit 57): określa, czy adresy wewnątrz lub poza granicami są chronione | |||

| 4 | 64-bitowe bity konserwacyjne: używane tylko do konserwacji | Główne miejsce do przechowywania rdzeni | |

| 5 | $CA | adres kanału (bity 12..18): tylko do odczytu, ustawiany przez „wymianę”, procesor we/wy | Rejestr tranzystorów |

| 6 | $CPU | inne bity procesora (bity 0..18): mechanizm sygnalizacji dla klastra do 20 procesorów | Rejestr tranzystorów |

| 7 | $LZC | liczba lewych zer (bity 17..23): liczba wiodących bitów zerowych z wyniku łącznego lub operacji zmiennoprzecinkowej | Rejestr tranzystorów |

| $AOC | all-ones count (bity 44..50): liczba bitów ustawionych w wyniku łącznym lub dziesiętna wielokrotność lub dzielenie | ||

| 8 | $L | Lewa połowa 128-bitowego akumulatora | Rejestr tranzystorów |

| 9 | $R | Prawa połowa akumulatora 128-bitowego | |

| 10 | $SB | bajt znaku akumulatora (bity 0..7) | |

| 11 | $IND | rejestr indykatorowy (bity 0..19) | Rejestr tranzystorów |

| 12 | $MASKA | 64-bitowy rejestr maski: bity 0..19 zawsze 1, bity 20..47 zapisywalne, bity 48..63 zawsze 0 | Rejestr tranzystorów |

| 13 | $RM | 64-bitowy rejestr reszty: ustawiany tylko przez instrukcje dzielenia liczb całkowitych i zmiennoprzecinkowych | Główne miejsce do przechowywania rdzeni |

| 14 | $FT | 64-bitowy rejestr współczynników: zmieniany tylko przez instrukcję „współczynnik obciążenia” | Główne miejsce do przechowywania rdzeni |

| 15 | $TR | 64-bitowy rejestr tranzytowy | Główne miejsce do przechowywania rdzeni |

| 16 ... 31 |

$X0 ... $X15 |

64-bitowe rejestry indeksowe (szesnaście) | Pamięć rdzenia indeksu |

Rejestry akumulatorów i indeksów działają w formacie znak-i-wielkość .

Pamięć

Pamięć główna to 16K do 256K 64-bitowych słów binarnych, w bankach po 16K.

Pamięć była chłodzona/ogrzewana zanurzeniowo w oleju, aby ustabilizować jej charakterystykę pracy.

Oprogramowanie

- Program montażu STRETCH (STRAP)

- MCP (nie mylić z Burroughs MCP )

- Języki programowania COLASL i IVY

- Język programowania FORTRAN

Zobacz też

- IBM 608 , pierwsze dostępne na rynku tranzystorowe urządzenie obliczeniowe

- ILLIAC II , tranzystorowy superkomputer z Uniwersytetu Illinois, który konkurował z firmą Stretch.

Uwagi

Bibliografia

Dalsza lektura

- Brooks, Fryderyk (2010). „Rozciąganie jest świetnym ćwiczeniem — zapewnia formę, by wygrywać”. Roczniki historii informatyki IEEE . 32 : 4–9. doi : 10.1109/MAHC.2010.26 . S2CID 43480009 .

Zewnętrzne linki

- Wywiad ustny z Instytutem Gene Amdahl Charles Babbage , University of Minnesota, Minneapolis. Amdahl omawia swoją rolę w projektowaniu kilku komputerów dla IBM, w tym STRETCH, IBM 701 , 701A i IBM 704 . Omawia swoją pracę z Nathanielem Rochesterem i kierownictwem IBM w procesie projektowania komputerów.

- IBM Stretch Collections @ Muzeum Historii Komputerów

- 7030 System Przetwarzania Danych (Archiwum IBM)

- IBM Stretch (znany również jako system przetwarzania danych IBM 7030)

- Szkic organizacji IBM Stretch

- Raport BRL dotyczący IBM Stretch

- Planowanie systemu komputerowego – Project Stretch , 1962 książka.

- Dokumenty IBM 7030 na Bitsavers.org (pliki PDF)