Plan piętra (mikroelektronika) - Floorplan (microelectronics)

W Electronic Design Automation , A floorplan się z układu scalonego jest schemat przedstawia wstępny umieszczeniu jej głównych bloków funkcjonalnych.

W nowoczesnym procesie projektowania elektronicznego plany pięter są tworzone na etapie projektowania pięter , na wczesnym etapie hierarchicznego podejścia do projektowania układów scalonych .

W zależności od zastosowanej metodologii projektowania, rzeczywista definicja planu piętra może się różnić.

Planowanie pięter

Planowanie podłóg uwzględnia pewne ograniczenia geometryczne w projekcie. Przykładami tego są:

- podkładki łączące do połączeń poza chipem (często przy użyciu połączeń drutowych ) są zwykle umieszczane na obwodzie chipa;

- sterowniki liniowe często muszą znajdować się jak najbliżej podkładek łączących;

- w związku z tym obszar wiórów ma w niektórych przypadkach minimalny obszar, aby zmieścić się w wymaganej liczbie klocków;

- obszary są grupowane w celu ograniczenia ścieżek danych, a zatem często zawierają określone struktury, takie jak pamięć podręczna RAM , mnożnik , przesuwnik baryłkowy , sterownik liniowy i jednostka arytmetyczno-logiczna ;

- zakupione bloki własności intelektualnej (bloki IP ), takie jak rdzeń procesora , są dostarczane w predefiniowanych blokach obszaru;

- Niektóre bloki IP mają ograniczenia prawne, takie jak zakaz trasowania sygnałów bezpośrednio nad blokiem.

Modele matematyczne i problemy optymalizacji

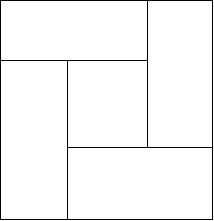

W niektórych podejściach plan piętra może być podziałem całego obszaru chipa na prostokąty ustawione w osi, które mają być zajęte przez bloki IC. Ten podział podlega różnym ograniczeniom i wymaganiom optymalizacji: obszar bloku, współczynniki kształtu , szacowana całkowita miara połączeń międzysieciowych itp.

Znalezienie dobrych planów pięter było obszarem badań w optymalizacji kombinatorycznej . Większość problemów związanych ze znalezieniem optymalnych planów pięter jest NP-trudnych , tj. Wymaga dużych zasobów obliczeniowych. Dlatego najczęstszym podejściem jest użycie różnych heurystyk optymalizacji w celu znalezienia dobrych rozwiązań.

Innym podejściem jest ograniczenie metodologii projektowania do określonych klas planów pięter, takich jak plany pięter podzielne.

Plany pięter podzielne

Plan piętra dzielony to plan piętra, który można zdefiniować rekurencyjnie, jak opisano poniżej.

- Plan piętra składający się z pojedynczego prostokątnego bloku można pokroić na plasterki.

- Jeśli blok z planu piętra dającego się przecinać jest przecinany („przecinany”) na dwie części za pomocą linii pionowej lub poziomej, wynikowy plan piętra można przecinać.

Plany pięter dzielone na segmenty były używane w wielu wczesnych narzędziach do automatyzacji projektowania elektronicznego z wielu powodów. Plany piętra przeznaczone do wycinania mogą być dogodnie reprezentowane przez drzewa binarne (a dokładniej drzewa k- d ), które odpowiadają kolejności cięcia. Co ważniejsze, wiele problemów NP-trudnych z planami pięter ma algorytmy czasu wielomianowego , gdy są ograniczone do planów pięter podzielnych.