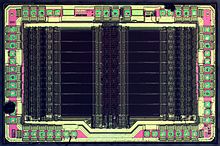

Kompleksowe programowalne urządzenie logiczne - Complex programmable logic device

Kompleks programowalne urządzenie logiczne ( CPLD ) jest programowalne urządzenie logiczne i złożoność pomiędzy niż Pals i FPGA i architektoniczne obu. Głównym elementem składowym CPLD jest makrokomórka , która zawiera logikę implementującą rozłączne wyrażenia postaci normalnej i bardziej wyspecjalizowane operacje logiczne.

Cechy

Niektóre funkcje CPLD są wspólne z PAL :

- Nieulotna pamięć konfiguracyjna. W przeciwieństwie do wielu FPGA, zewnętrzna pamięć ROM konfiguracji nie jest wymagana, a CPLD może działać natychmiast po uruchomieniu systemu.

- W przypadku wielu starszych urządzeń CPLD routing ogranicza większość bloków logicznych, aby sygnały wejściowe i wyjściowe były podłączone do zewnętrznych styków, co zmniejsza możliwości wewnętrznego przechowywania stanu i głęboko warstwowej logiki. Zwykle nie jest to czynnik w przypadku większych CPLD i nowszych rodzin produktów CPLD.

Inne cechy są wspólne z FPGA :

- Dostępna duża liczba bram. CPLD zazwyczaj mają odpowiednik tysięcy do dziesiątek tysięcy bramek logicznych , co pozwala na implementację umiarkowanie skomplikowanych urządzeń do przetwarzania danych. PAL zazwyczaj mają co najwyżej kilkaset równoważników bramek, podczas gdy FPGA zwykle wahają się od dziesiątek tysięcy do kilku milionów.

- Niektóre postanowienia dotyczące logiki bardziej elastycznej niż wyrażenia sumy iloczynu , w tym skomplikowane ścieżki sprzężenia zwrotnego między komórkami makr oraz wyspecjalizowana logika do implementowania różnych powszechnie używanych funkcji, takich jak arytmetyka liczb całkowitych .

Najbardziej zauważalną różnicą między dużym CPLD a małym FPGA jest obecność w chipie nieulotnej pamięci w CPLD, która pozwala na użycie CPLD do funkcji " boot loader " przed przekazaniem sterowania innym urządzeniom, które nie mają ich własne stałe przechowywanie programu. Dobrym przykładem jest sytuacja, w której CPLD jest używany do ładowania danych konfiguracyjnych dla FPGA z pamięci nieulotnej.

Wyróżnienia

CPLD były ewolucyjnym krokiem w stosunku do jeszcze mniejszych urządzeń, które je poprzedzały, PLA (po raz pierwszy dostarczonych przez Signetics ) i PAL . Te z kolei były poprzedzone standardowymi produktami logicznymi , które nie oferowały programowalności i służyły do budowania funkcji logicznych poprzez fizyczne połączenie kilku standardowych układów logicznych (lub setek) razem (zwykle za pomocą okablowania na płytce drukowanej lub płytkach, ale czasami, szczególnie do prototypowania, przy użyciu okablowania owijanego drutem ).

Główna różnica między architekturami urządzeń FPGA i CPLD polega na tym, że układy FPGA są wewnętrznie oparte na tablicach przeglądowych (LUT), podczas gdy układy CPLD tworzą funkcje logiczne z morzem bramek (na przykład sumą produktów).

Zobacz też

- Język:

- Producenci:

- Altera (teraz Intel)

- Półprzewodnik cyprysowy

- Półprzewodnik sieciowy

- Microchip (dawniej Atmel )

- Xilinx

- Technologia:

- Układ scalony specyficzny dla aplikacji (ASIC)

- Kasowalne programowalne urządzenie logiczne (EPLD)

- Proste programowalne urządzenie logiczne (SPLD)

- Macierz makrokomórek

- Programowalna logika tablicy (PAL)

- Programowalna tablica logiczna (PLA)

- Programowalne urządzenie logiczne (PLD)

- Ogólna logika tablicy (GAL)

- Programowalna logika kasowalna elektrycznie (PEEL)

- Programowalna macierz bramek (FPGA)